ISSN (Print): 0974-6846 ISSN (Online): 0974-5645

# Linear Peak Current Mode Control of Semi Bridgeless AC-DC Converter

#### Shaik Ahmad Hussain\* and G. Kanimozhi

School of Electrical Engineering, VIT University, Chennai - 632014, Tamil Nadu, India; hussain786rockz@yahoo.com, kanimozhi.g@vit.ac.in

#### **Abstract**

**Objectives:** The main objective of this work is to obtain input power factor closer to unity and regulation of output voltage of semi bridgeless AC-DC converter using linear peak current mode control. **Methods/Statistical Analysis:** Linear Peak Current Mode control technique is applied to Semi-Bridgeless AC-DC Converter in this paper. This technique helps in achieving power factor closer to unity. The output voltage of the converter is regulated at 200V. The prototype is designed for 200W. Simulation results are obtained for 200W using PSIM software (Simulation Software Package) the converter is analyzed under variable load and supply conditions. **Findings:** At variable load conditions, power factor is maintained closer to unity and output voltage is regulated to 200V. The efficiency for the converter is found to 96% at full load conditions. **Application:** Battery charging applications.

Keywords: AC-DC Converter, Compensating Ramp, Phase Shifting, Peak Current Mode, Semi-Bridgeless

# 1. Introduction

Generally, switching converters operate in three conduction modes, continuous conduction mode (CCM), discontinuous conduction mode (DCM) and critical conduction mode (CrCM). CCM operation is useful in high power converters because they require high inductance values and sub harmonics oscillations elimination<sup>1</sup>. DCM is advantageous for low power converters. They require low inductance values compared to CCM and sub harmonics do not appear. Up to few hundred watts, these three conduction modes apply. In particular, upto half kilowatt, CCM and CrCM are implemented2. Above kilowatt, CCM becomes a better solution. CCM also holds the advantages of lower noise, lower conduction losses. Losses of reverse recovery also show a downfall in CCM. But CCM operated rectifier exhibit greater complexity compared to CrCM and DCM.

In derived converters, change in modes of operation from CCM to DCM, the system changes from second order to first order<sup>3</sup>. CrCM of a switching converter is

operated at the boundary between CCM and DCM. Generally, in a CrCM, on-time of the switch is fixed with variable off time. The proposed semi bridgeless converter operates in discontinuous conduction mode as inductor current touches zero between switching cycles.

The converter involves a delay between the pulses provided to the gate terminals of the two switches. Gating voltage to the second switch is 180° phase shifted from the first switch. This phase shifted gating helps in current synthesizing and simultaneously brings out input current shape<sup>4</sup>. In this paper, linear peak current mode (LPCM) control is applied to Semi bridgeless AC-DC converter. Since the converter operates in DCM, the control technique applied also operates in DCM. In LPCM, the peak value of the inductor current is sensed whereas in conventional average current mode control, the average value of inductor current is sensed<sup>5</sup>. The proposed converter is used in battery charging applications since it can afford high efficiency at light loads so that charging time, charging cost, amount and cost of electricity can be minimized6.7.

<sup>\*</sup>Author for correspondence

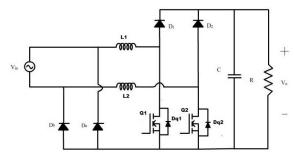

# 2. Semi Bridgeless PFC Converter

AC-DC conversion requires a rectifier which consists of four diodes, aligned two in parallel. Semi-bridgeless<sup>8</sup> comprises of two slow diodes Da and Db as shown in Figure 1. These two diodes connect the output to the PFC ground. Their function is to reduce EMI related issues<sup>2</sup>. These diodes do not have continuous conduction of current. Hence, their conduction losses are less. Q1 and Q2 are the MOSFET's in the converter as shown in Figure 1. D1 and D2 are the normal diodes used for forward conduction of current. Dq1 and Dq2 are the body diodes of the switches D1 and D2 respectively. In this converter, most of the current passes through the body diodes of the switches. Hence, for such a topology, switches are to be chosen in such a way that their body diodes withstand higher values of current<sup>10</sup>. Compared to conventional topologies like bridgeless PFC and dual boost topology, this converter avoids the problem of input floating<sup>12</sup>. The gating pulse for switch Q1 is denoted as Vg1 and the gating pulse for switch Q2 is denoted as Vg2.

### 2.1 Modes of Operation

The circuit operation is analysed with four different modes. The modes of operation described apply for converter with duty cycle less than 0.5. The operation of the converter in positive half cycle is presented as follows.

Figure 1. Phase Shifted Semi Bridgeless converter.

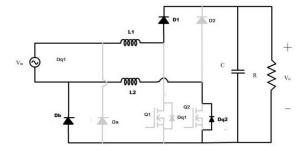

Figure 2(a). Q1 and Q2 OFF, Q2 body diode conducting.

Figure 2(b). Q1 ON, Q2 body diode conducting.

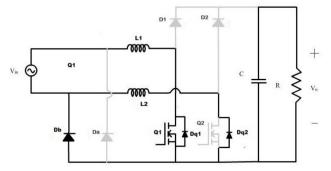

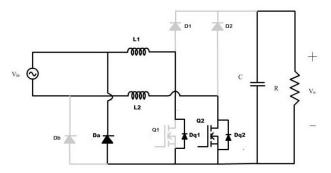

Figure 2(c). Q1OFF, Q2 ON.

### Interval 1 [ *t*0 - *t*1 ]:

At time interval  $t_0$ , both the switches  $Q_1$  and  $Q_2$  are OFF. In this interval, the energy stored in the intervals  $L_1$  and  $L_2$  is sent to output through the path of  $L_1$ ,  $D_1$ ,  $D_1$ ,  $D_2$ ,  $L_2$  and  $D_2$  as shown in Figure 2(a).

#### Interval 2 [t1-t2]:

At interval t1, Q1 is ON and Q2 is OFF. The currents in the inductors L1 and L2 increase linearly and energy is stored in the inductors. The voltage across the capacitor C appears across the load. Db and Dq2 shares the return current as shown in Figure 2(b).

#### Interval 3 [t2-t3]:

Interval 1 is repeated here. Both the switches are OFF here. The energy in the inductors is released in the path of L1, D1, Dq2, L2 and Db as illustrated in Figure 2(a).

### Interval 4[ *t*3 - *t*4 ]:

In this interval, Q1 is OFF and Q2 is ON. The energy in the inductors is released in the path of L1, D1, Q2, Dq2, L2 and Db as shown in Figure 2(c).

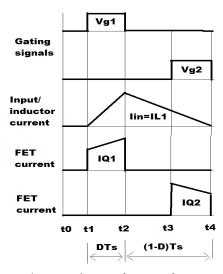

The operation of negative half cycle is similar to that of positive half cycle. The theoretical waveforms of the converter are presented in Figure 3.

**Figure 3.** Theoretical waveforms of Semi Bridgeless converter.

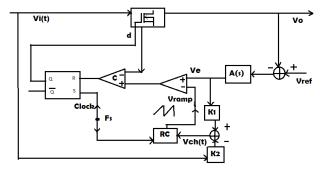

#### 2.2 Linear Peak Current Mode Control

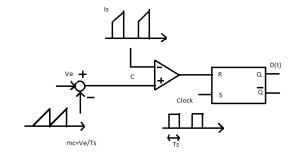

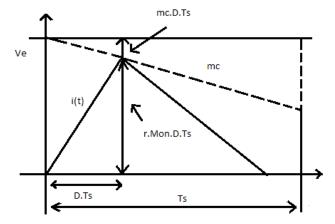

Linear peak current mode control is applied to both CCM and DCM operations 12-16. The operation of LPCM in DCM is illustrated in Figure 4. The aim of this control technique is to modify the shape of input current in phase with input voltage at lower conversion ratios. Three signals considered for analysis are the output voltage feedback signal; the input voltage feed forward signal and the switching current signal. The slope of the compensating ramp helps to achieve power factor correction which depends on both the output voltage feedback signal and the input voltage feed forward signal. Duty cycle is modulated based on the slope variation of the ramp signal. A voltage error signal Ve is obtained from the comparison of output voltage Vo and voltage reference, Vref. This signal is compared with the compensating ramp and the output of comparator is fed to set-reset flip flop. The compensating ramp ensures stability of feedback loop and power factor correction. The compensating ramp also suppresses sub-harmonic oscillations. The compensating ramp is shown in Figure 5. LPCM holds a control law for the modulation of duty cycle.

The proposed control law is derived as follows: Let  $m_c$  be slope of the compensating ramp, Ve be the voltage of the output error,  $m_{on} = Vi/L$ , where L is the inductance of the converter, Vi(t) be the input AC voltage and R is the resistance of the converter. From the analysis, slope of compensating ramp  $m_c$  is obtained from the expression,

$$V_e - m_c D T_s = r m_{on} D T_s \tag{1}$$

Figure 4. Linear peak current mode controller.

**Figure 5.** Compensating Ramp in DCM.

Where  $T_s$  be the switching period, r is gain of current sensor of the switch and on simplifying,

$$mc = \frac{Ve}{DTs} - rmon \tag{2}$$

In terms of conversion ratio M', m<sub>c</sub> is written as

$$mc = \frac{F(M')Ve}{DxTs} - rmon \tag{3}$$

where

$$F(M') = \frac{1}{\sqrt{1 - M'(t)}}$$

(4)

and

$$M'(t) = \frac{Vi(t)}{Vo}$$

(5)

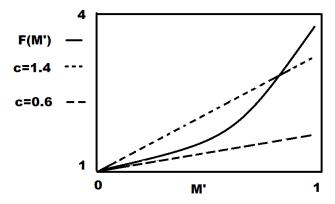

For a boost converter, the input voltage is always less than output voltage. To satisfy this, M'(t) should be less than 1 in the whole period. In terms of Taylor's expansion and considering first two terms, F(M') is written as

$$F(M') \cong 1 + cM'(t) \tag{6}$$

Here coefficient c is chosen to be good approximation for M' (t)<0.5. c=0.5 is the approximate value.(Refer Figure. 6). In case, if duty cycle is expressed as function of time then,

$$D(t) = D_x \sqrt{1 - M'(t)} \tag{7}$$

Where

$$Dx = \frac{\sqrt{4V0^2 L}}{\sqrt{Vi^2 RTs}}$$

(8)

Approximated control law is

$$D_a(t) = \frac{D_x}{1 + cM'(t)} \tag{9}$$

Then approximated slope of compensating ramp becomes

$$mca = \frac{Ve}{DxTs} + Vi(t)\left[\frac{Vec}{DxTs} - \frac{r}{L}\right]$$

(10)

Figure 7 shows the slope of ideal and approximated compensating ramps when Vi(t) varies for different values of Ve, Ve1 and Ve2. This helps in choosing better Ve for design of voltage error amplifier. D is ideal duty cycle whereas Da and m<sub>ca</sub> are the approximated duty cycle and approximated compensating ramp respectively. Generated voltage signal for compensating ramp implementation is

$$V_{ch}(t) = m_{ca}T_s \tag{11}$$

Under steady state conditions,

$$V_{ch}(t) = K_1 V_e + K_2 V_i(t)$$

$$\tag{12}$$

Where constants

$$K_1 = \frac{1}{D_x} \tag{13}$$

$$K_{2} = \frac{1}{T_{s}} \left[ \frac{V_{e}C}{D_{x}T_{s}V_{0}} - \frac{r}{L} \right]$$

(14)

**Figure 6.** Approximation in the Compensating Ramp.

**Figure 7.** Slope of ideal and approximating compensating ramps.

K2 could be either positive or negative value. But to depict the shape of compensating ramp, it is chosen negative. For the implementation of control law, a basic block diagram is shown in Figure 8. A signal Ve is obtained through a low pass filter A(s) to which the output error is provided. Simultaneously from RC circuit, a signal Vch(t) is applied. This signal is obtained by the combination of output error voltage Ve and input signal Vi(t). At the two inputs of the op-amp, the error signal and the generated ramp are applied. The signal from the current sensor of the switch and the output of the op-amp are compared to modulate the duty cycle through a Set-Reset flip flop.

Figure 8. Basic Block Diagram of LPCM.

# 4. Simulation Results

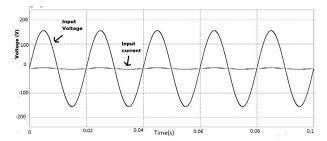

Simulation for this proposed control technique to the converter is done using PSIM. The converter specifications are shown in Table 1. Figure 9 shows input voltage and input current waveforms for full load condition. It is observed that PF is around 0.96. The value of input voltage and input current are 110V (peak to peak) and 5A (peak to peak) respectively.

Table 1. Converter Specifications

| Parameter                | Range    |

|--------------------------|----------|

| Input Voltage (Vin)      | 110V rms |

| Output Voltage (Vo)      | 200V DC  |

| Inductors L1,L2          | 1.3mH    |

| Output Capacitor, C      | 470μF    |

| Resistive Load, R        | 200Ω     |

| Output Power             | 200W     |

| Switching Frequency, Fsw | 70KHz    |

Figure 9. Input current and Input voltage waveforms.

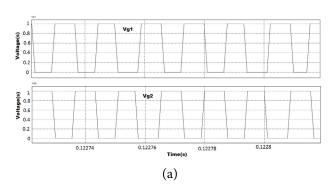

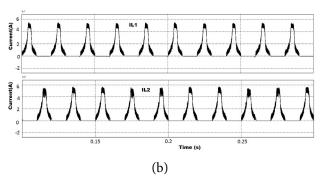

**Figure 10.** (a) Gating pulses to switches Q1 and Q2 (b) Inductor currents IL1 and IL2.

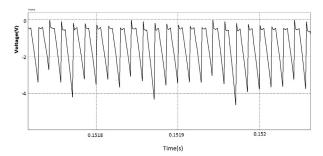

The gating pulses obtained from Set-Reset flip-flop is 70 KHz.A delay of  $7.14 \mu \text{S}$  is provided between the switches to get the required phase shift of  $180^{\circ}$ . The shift could be viewed in Figure 10(a). The inductor currents

has a peak value of around 5A. Figure 10(b) shows the charging and discharging patterns of inductor currents executed as modes of operation in shown in section II. The output voltage has a value of 230V as shown in Figure 11(a). This voltage is observed across a resistor of  $200\Omega$  and the output current has a value of around 1A as shown in Figure 11(b).

**Figure 11.** (a) Output Voltage waveform (b) Output current waveform.

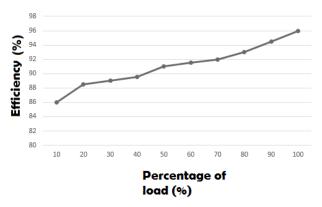

The voltage signal shown in Figure 12 is obtained from the integrator to which the inputs are inductor current sensed and error output voltage. The value is around -20V. The efficiency of the converter is observed for variable loads and is plotted as Figure 13. Maximum efficiency obtained at full load is 96%. Compared to average current mode control, LPCM exhibits good efficiency at low loads.

# 4. Conclusion

Linear peak current mode control for semi bridgeless AC-DC converter for power factor correction and voltage regulation is proposed. From the simulation results, it is inferred that a good power factor is achieved and output voltage is regulated at variable load conditions. With the use of LPCM technique, circuit implementation is sim-

plified and low cost standard PWM controller is utilized. This technique could also be applied to continuous conduction mode for better results.

Figure 12. Compensation of ramp.

Figure 13. Efficiency Vs Load.

## 5. References

- Lazar J, Cuk S. Open Loop Control of Unity Power factor Discontinuous Conduction mode Boost Rectifier. IEEE Telecommunications Energy Conference, Netherlands. 1995. P. 671–77.

- Gegner JP, Lee CQ. Linear Peak Current Mode Control: A Simple Power Factor Correction Control Technique for CCM. IEEE PESC Records. 1996; 1:196–202.

- 3. Kanimozhi G, Sreedevi VT. ZVS Implementation in Interleaved boost rectifier. ARPN Journal of Engineering and Applied Sciences. 2015 Sep; 10(16):1–6.

- Musavi F, Eberle W, Dunford WG. A Phase-Shifted Gating Technique with Simplified Current Sensing for the Semi-Bridgeless AC-DC Converter. IEEE Transactions on Vehicular Technology. 2013 May; 62(4):1568-76.

- Shin JW, Cho BH. Digitally Implemented Average Current-Mode Control in Discontinuous Conduction Mode PFC

- Rectifier. IEEE Transactions on Power Electronics. 2012 Jul; 27(7):3363-73.

- 6. Musavi F, Edingto M, Eberle W, Dunford WG. Evaluation and Efficiency Comparison of Front End AC-DC Plug-in Hybrid Charger Topologies. IEEE Transactions on Smart grid. 2012 Mar; 3(1):413–21.

- Lee YJ, Khaligh A, Emadi A. Advanced Integrated Bidirectional AC/DC and DC/DC Converter for Plug-In Hybrid Electric Vehicles. IEEE Transactions on Vehicular Technology. 2009 Oct; 58(8):3970–80.

- Sudheer L, Kanimozhi G. Integrator controlled semibridgeless PFC boost converter. International Conference on Circuit, Power and Computing Technologies, India. 2015 Mar. p. 1–5.

- Brown R, Soldano M. One Cycle Control IC Simplifies PFC Designs. APEC 05, 2014; 1–5.

- Akter P, Uddin M, Rahman M, Islam M, Bhuiyen RB. Efficiency Improvement of Semi-Bridgeless Phase Shifted Boost Converter with Power Factor Correction in Energy Storage System. International Conference on Electrical Information and Communication Technology (EICT), Khulna. 2014 Feb. p. 1–5.

- Alonge F, Librizzi F, Raimondi FM, Scalia P, Uno A. Improved peak-current-mode control for unity power factor ac-dc converters in discontinuous conduction mode. IEEE International Conference on Power Electronics and Drive Systems- PEDS'99. Hong Kong. 1999 Jul. p. 927–32.

- Basso C. Ramp Compensation for Current-Mode Converters, Power design, Circle 252 on Reader Service Card or freeproductinfo.net/pet, Power Electronics Technology. 2004 Jul; 67–8.

- 13. Kim SY, Sung WY, Lee BK. Comparative Performance Analysis of High Density and Efficiency PFC Topologies. IEEE Transactions on Power Electronics. 2014 Jun; 29(6):2666–79.

- Kim HJ, Seo G-S, Cho B, Choi H. A Simple Average Current Control with On-Time Doubler for Multiphase CCM PFC Converter. IEEE Transactions on Power Electronics. 2015 Mar; 30(3):1683–93.

- Choi WY, Kwon JM, Kim EH, Lee JJ, Kwon BH. Bridgeless Boost Rectifier with Low Conduction Losses and Reduced Diode Reverse-Recovery Problems. *IEEE Transactions on Industrial Electronics*. 2007 Apr; 54(2):769–80.

- Kumar GS, Kanimozhi G, Sreedevi VT. Comparative analysis of digital linear and nonlinear controller for PFC boost converter. International Journal of Applied Engineering Research. 2015; 10:15689–93.