# PAPER • OPEN ACCESS

# Design and Implementation of Low Power High Stability 8T SRAM

To cite this article: R Harshni and V Ravi 2020 J. Phys.: Conf. Ser. 1716 012038

View the article online for updates and enhancements.

This content was downloaded from IP address 106.195.40.208 on 06/08/2021 at 08:05

Journal of Physics: Conference Series

# **Design and Implementation of Low Power High Stability 8T SRAM**

# R Harshni<sup>1</sup> and V Ravi<sup>1\*</sup>

<sup>1</sup>School of Electronics Engineering, Vellore Institute of Technology, Chennai, India <sup>\*</sup>ravi.v@vit.ac.in

**Abstract.** This paper examines about the power decrease system in a memory cell. It affords a low power high stability 8T Static Random Access Memory (SRAM) cell. Two typically used SRAM cells are analyzed in phrases of their stability and power. It presents improved performance as analyzed with traditional 6T SRAM cell in terms of leakage power and static noise margin. The scheme of low power 8T SRAM is executed along enforcing power gating approach. Power gating is executed with the aid of putting a transistor in between the 8T SRAM cell and VDD or ground. However, this avoids the direct VDD and ground path and forming an indirect VDD and indirect ground path. The static noise margin of 8T SRAM is computed to decide higher stability whilst compared with 6T SRAM. It is inferred that the power of the newly programmed 8T SRAM cell is diminished close to 1.5% as contrasted with that of the traditional 8T SRAM cell and the stability is improved close to 8.19%.

### 1. Introduction

The present mechanically associated world creates various measure of information and the innovation engaged with regular application is essential to process and preserve this colossal measure of information. Memory happens to be a necessary piece of every electronic gadget for putting away guidelines or information created by calculation [1]. The regularly utilized memory type is the SRAM cell. This cell is equipped for putting away single piece of information insofar as power is provided to the cell and doesn't need intermittent reviving as on account of the DRAM's. The low power uses, for example, designed biomedical gadgets, portable gadgets requests higher energy efficiency to accomplish broad battery life[10]. The SRAM memory is utilized as reserve memory in super PCs and workstations due to low power and fast activity. The leakage current involves a rate which is more than 40 % of vitality utilization in the superior IC's. SRAM memory cluster in SOC adds to a large portion of spillage and also subsequently planning a low leakage and less power expending memory square is attractive. Moreover, the solidness of the memory cell for composing and perusing the bit put away is of convey and with diminished inventory voltage supply, the defer increments [11].

Consequently, a fair strategy should be utilized to diminish leakage power, power utilization and increment stability of the cell. The most normally utilized 6T SRAM cell has the detriment of keeping up essential Read Noise Margin (RNM) and Write Noise Margin (WNM) as the innovation is downsized. To conquer this, SRAM cells with 7T, 8T and 9T were built to cast and accomplish preferable outcomes over the regular 6T cell.

| National Science, Engineering and Technology | Conference (NCSET) 20     | 20 IOP Publishing                   |

|----------------------------------------------|---------------------------|-------------------------------------|

| Journal of Physics: Conference Series        | <b>1716</b> (2021) 012038 | doi:10.1088/1742-6596/1716/1/012038 |

# 2. Literature Survey

Numerous examinations had been done to diminish the power consumption in SRAM, to improve less power and energy proficient SRAM. A considerable lot of these spread SRAMs worked at low voltages decreasing power dissipation, SRAMs utilizing systems like power gating in which the circuits are turned off when they are not required, SRAMs where the power supply voltage is diminished to a lower an incentive during reserve mode and SRAMs dependent on adiabatic procedures[7]. Bringing down the power supply voltage diminishes the dynamic power quadratic partner and leakage power exponentially. Be that as it may power supply voltage scaling additionally confines signal swing and hence decreases noise margin. Further, forceful innovation scaling in the sub-100nm locale builds the affectability of the circuit parameters to process variation (PV)[3]. Leakage currents are chiefly because of gate leakage current and sub threshold leakage current. High K gate technology diminishes the gate leakage current. Forward body biasing strategies and double Vt methods are used to decrease sub threshold leakage current. Jaydeep P. Kulkarni et.al proposed Schmitt Trigger SRAM cell that fuses an implicit criticism component, accomplishing 56 % improvement in SNM, improvement in process variety resistance lower read disappointment likelihood, low-voltage/low power activity, also, improved information maintenance ability at ultralow voltage contrasted with ordinary 6T SRAM cell. They report that at iso-region and iso-readdisappointment likelihood the proposed memory bit cell works at a lower (175 mV) VDD with 18% decrease in leakage and half decrease in read/compose power contrasted with the customary 6T cell. According to their reenactment results, the proposed memory bit cell holds information at a supply voltage of 150 mV. Naveen Verma et.al presented 8T bit-cell with buffered read which disposes of the read SNM limitation.

Added to it the fringe footer circuit wipes out bit line leakage. The peripheral write drivers and storage-cell supply drivers structured by the writers connect to lessen the phone supply voltage during compose tasks. Sense-amp repetition gave produces a good exchange off among balance and region. The SRAM cluster worked with 65nm innovation was found to be useful at 350mV and information accurately held at 300mV [13]. Fatih Hamzaoglul et.al introduced a 153Mb SRAM configuration upgraded for 45nm high – K metal-entryway innovation.

The plan as set forward by the creators contains completely coordinated dynamic forward-body - inclination to accomplish lower voltage activity while keeping low the territory and force overhead. The dynamic rest configuration utilized with operation amp - put together criticism control and with respect to bite the dust programmable reference voltage generator decreases the impact of procedure varieties and lessens the power. They guarantee that the plan works over 4.5GHZ at 1.1V and the more grounded PMOS under the forward body predisposition improves the working voltage up to 75mV, without expanding the leakage power.

The high K material nearly dispenses with gate leakage in the cell and makes this plan appealing for low power uses. Y. Wang et.al proposed a 1.1 GHz 12  $\mu$ A/Mb SRAM plan in 65nm ultra–low power CMOS innovation with incorporated leakage decrease method for portable applications. They utilize entryway oxide thickness improvement and door nitridation to lessen entryway leakage. Well and pocket inserts and source channel spacers happen to be streamlined at the same time to lessen sub edge spillage. Separate Vt limit voltage control for the N and P transistors in various SRAM cells and fringe circuit is utilized to get least Vmin. The cell measurement is streamlined to get high exhibit proficiency of 78% and bit efficiency of 115Mb/cm2 for 128kb sub array with improved static noise margin, write margin and read current at low-voltage configuration point Transistor stacking what's more, the long channel transistors are utilized to spare sub leakage in fringe circuits. As revealed it accomplishes 1.1 GHz frequency at an ostensible voltage of 1.2V and 250MHZ at 0.7V which is professed to be the most elevated announced frequency for a similar class of reserve power utilization for portable applications.

| National Science, Engineering and Technology | Conference (NCSET) 202 | 20 IOP Publishing                   |

|----------------------------------------------|------------------------|-------------------------------------|

| Journal of Physics: Conference Series        | 1716 (2021) 012038     | doi:10.1088/1742-6596/1716/1/012038 |

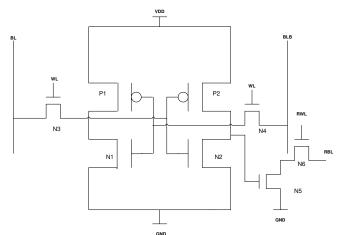

#### 3. Architecture of SRAM

SRAM cell happens to be the center component in the SRAM cluster. Every cell contains a solitary piece of data. The SRAM cell doesn't need intermittent reviving as long as the supply is given to the SRAM cell. It gives consistent peruse and compose tasks to be acted in it. The conventional 6T SRAM cell contains two cross coupled inverters associated with corresponding piece lines by means of access transistors. The data to be put away is composed by means of these entrance transistors and the data to be perused is finished by associating the reciprocal piece lines to the sense speaker. The Static Noise Margin (SNM) gives a measurement to the steadiness of SRAM cell architecture. The SNM data canibe determined for three unique tasks of the SRAM, namely the READ, WRITE and the HOLD activity. The SNM diagram is drawn by inferring the VTC bend of the two inverters in the cell and these outcomes in a two-lobed bend known as the butterfly bend [12-15]. The biggest conceivable square that can be obtained from the curve gives stability information. The conventional 6T SRAM structure is generally utilized in light of the fact that of extremely less area utilization. Notwithstanding, it shows extremely low read and write stability and this thusly, looks for structure of a powerful SRAM cell. The 8T SRAM cell be that as it may has two decoupled ways for peruse and compose activity to be performed. This shows great peruse and compose strength and subsequently ends up being a superior alternative for planning the SRAM exhibit. The 8T SRAM cell comprises of two bit lines (BL and BLB) associated via the two NMOS get to transistors what's more, the hub where bit is put away is associated with the entryway of another transistors whose source is associated with ground [17]. The channel of this transistor is associated with wellspring of different transistor and control line for read activity is sent to the entryway of this transistor known as the Read Word Line (RWL). The Read Bit Line, also known as RBL gives the read yield and this line is precharged before being perused. Whenever bit 1 is composed via BL, it makes the transistor N5 ON and when RWL is given then transistor N6 turns ON, depleting the charge put away in RWL providing a correlative yield. It is appeared in the Figure 1.

Figure 1. Conventional 8T SRAM cell

#### 4. Power

Power alludes to the quantity of Joules disseminated over a specific measure of time .While energy is a proportion of the complete number of Joules disseminated by a circuit. Carefully, low-power configuration is an alternate objective from low-energy structure in spite of the fact that they are connected. Power is an issue essentially when cooling is a worry.

The most extreme power at any time, peak power, is regularly utilized for power and ground wiring configuration, signal noise margin and reliability analysis [4]. Energy per activity or task is a superior measurement of the energy efficiency of a framework, particularly in the space of augmenting battery lifetime. Power enhancement is the utilization of electronic structure mechanization devices to upgrade (diminish) the power utilization of computerized structure, for example, that of combinational circuits, an incorporated circuit, while protecting the usefulness [6]. Power can be

National Science, Engineering and Technology Conference (NCSET) 2020IOP PublishingJournal of Physics: Conference Series1716 (2021) 012038doi:10.1088/1742-6596/1716/1/012038

assessed at various degrees of detail. The more elevated degrees of deliberation are quicker and can manage bigger circuits, yet are less precise [8]. The fundamental levels include: Circuit Level Power Estimation, utilizing a circuit test system, for example, SPICE Static Power Estimation doesn't utilize the info vectors, yet may utilize the information insights. Similar to static timing analysis, Logic-Level Power Estimation frequently connected to logic simulation. Examination at the Register-Transfer Level is quick and high limit, however not as precise. The requirement for low power integrated circuits is well known due to their broad use in the electronic versatile supplies. On chip SRAMs (Static Random Access Memory) decide the power dissemination of SoCs (System on Chips) notwithstanding its speed of activity. Thus it is important to have energy efficient SRAMs. Heft of the energy in SRAMs is squandered during charging of the bit lines and releasing it to the ground during peruse and compose activities. SRAM cell other execution qualities like read stability, write ability, read and write delay and so forth have been found by simulation not withstanding vitality sparing under fluctuated states of memory tasks[18, 19]. The impact of gadget parameters of the driver on total energy of the SRAM cell has been explored. Further examinations secured proposed SRAM cell exhibits. So as to build vitality sparing further, the chance of having adiabatic SRAM with single bit line for reading and writing is analyzed.

#### **5.** Power Reduction Technique

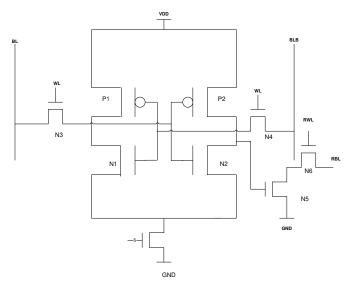

The plan of low power SRAM is accomplished by executing various procedures, to be specific powerigating and Multi Threshold CMOS (MTCMOS) method. Power gating is accomplished by setting a transistor in the middle of the SRAM cell and VDD or ground (gnd). Subsequently, this refutes the direct VDD and ground way and making an indirect VDD and indirect ground way.

The MTCMOS system utilizes the sleep transistors of high edge esteem which supports in lessening the leakage power iin ithe general circuit. At the point when the circuit is in HOLD mode, the sleep transistors behave as a switch, thereby removing the power. Power gating should be possible by two methods, by putting a PMOS transistor between theimemory cell what's more, VDD or by putting NMOS transistor between memory cell what's more, ground [2]. Henceforth, MTCMOS procedure gives huge change as far as power decrease in the circuit.

Figure 2. Power Gating Implementation in 8T SRAM cell

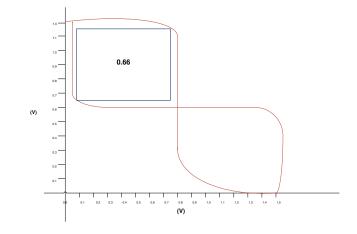

#### 6. Static Noise Margin

For the most part, the insusceptibility of SRAM cell to static noise is communicated as far as Static Noise Margin (SNM). It is characterized to be the most extreme estimation of the DC noise voltage that can be endured by SRAM cell by not changing the put away bits. Precisely, the SNM of 6T SRAM cell can be analyzed by plotting the DC attributes of an inverter and reflecting it [9]. At that point discovering the most extreme conceivable square in

between them. This graphical strategy for discovering SNM is known as "butterfly bend". As the innovation scaling, cell turns out to be less steady with lower working voltage, expanding leakage flows. Similarly the static noise margin of 8T SRAM cell can be analyzed by plotting the DC attributes of a CMOS inverter and reflecting it. Cell turns out to be less steady during read activity, as a result of the voltage separating impact at the inverter which stores 0, will be turned on. The downside of SNM metrical utilizing butterfly bend is that it doesn't consists of programmed in-line analyzers [5]. To determine the Static Current Noise Margin (SINM), still it needs numerical control from the deliberate information. Though, the N-bend consists of the data of both read soundness and compose capacity, in this way it survives the impediments of SNM metric utilizing butterfly bends.

# 7. Results and Conclusion

bib

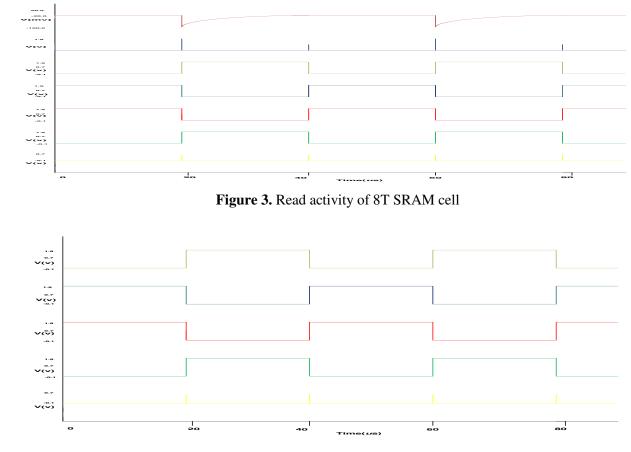

The read and write operations of 8T SRAM cell are shown in Figure 3 and Figure 4.

Figure 4. Write activity of 8T SRAM cell

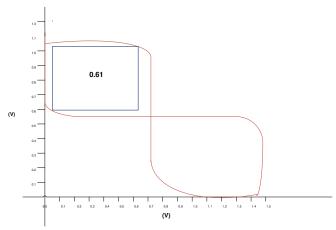

The stability of 8T and 6T SRAM are determined using the Static Noise Margin (SNM). It is shown in Figure 5 and Figure 6 respectively.

**IOP** Publishing

Journal of Physics: Conference Series

**1716** (2021) 012038 doi:10.1088/1742-6596/1716/1/012038

Figure 5. Static Noise Margin (SNM) of 8T SRAM cell.

Figure 6. Static Noise Margin (SNM) of 6T SRAM cell

Table 1 Comparison of Power Gating Technique in 6T and 8T SRAM cells

| Without Power | With Power                     |

|---------------|--------------------------------|

| Gating        | Gating                         |

| Technique     | Technique                      |

| 1.032mW       | 1.014mW                        |

| 0.6418nW      | 0.6363nW                       |

|               | Gating<br>Technique<br>1.032mW |

The power gating technique in 6T and 8T SRAM architectures are tabulated in Table 1. It is understood that power is reduced in 8T SRAM cell using power gating technique.

Stability happens to be a significant problem in rapid CMOS VLSI plan. In this paper, a low power consuming and a highly stable SRAM cell has been proposed and programmed.

It is inferred that the power of the proposed 8T SRAM cell is diminished close to 1.5% as contrasted with the traditional 8T SRAM cell and the stability is improved close to 8.19%.

# 8. References

- [1] Singh P and Kumar Vishvakarma S 2018 Ultra-Low Power High Stability 8T SRAM for Application in Object Tracking System in IEEE Access 6 2279-2290

- [2] Wu et al. 2016 A 0.35 V 375 40 nm 128 kb symmetrical 10T subthreshold SRAM with tristate bit-line Microelectron 51 89-98

- [3] Kushwah C B, Vishvakarma S K and Dwivedi D 2016 Single-ended boost-less (SE-BL) 7T process tolerant SRAM design in sub-threshold regime for ultra-low-power applications Circuits Syst. Signal Process 35 385-407

- [4] Moghaddam M, Timarchi S, Moaiyeri M H and Eshghi M 2016 An ultra-low-power 9T SRAM cell based on threshold voltage techniques Circuits Syst. Signal Process 35 1437-1455

- [5] Chen J, Chong K S and Gwee B H 2015 Ultra-low power read-decoupled SRAMs with ultralow write-bitline voltage swing Circuits Syst. Signal Process., 33 3317-3329

- [6] Liang Wen, Zhentao Li and Yong Li 2013 Single-ended, robust 8T SRAM cell for lowvoltage operation in Elsevier 44 718-728

- [7] Alioto M 2012 Ultra-low power VLSI circuit design demystified and explained: A tutorial IEEE Trans. Circuits Syst. I, Reg. Papers 59 3–29

- [8] Chen et al. 2010 Millimeter-Scale Nearly Perpetual Sensor System with Stacked Battery and Solar Cells in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers 288-289

- [9] Hanson et al. 2009 A Low-Voltage Processor for Sensing Applications with Picowatt Standby Mode IEEE J. Solid-State Circuits 44 1145-1155

- [10] Naveen Verma and Anantha P Chandrakasan 2007 A 65nm 8T Sub-Vt SRAM Employing Sense-Amplifier Redundancy Proc. Of International Solid State Circuits Conference 328-329

- [11] Calhoun B H and Chandrakasan A 2006 A 256 kb sub-threshold SRAM in 65 nm CMOS iIEEE Int. Solid State iCircuits Conf. (ISSCC) Dig. Tech. 2592-2601

- [12] Lin C P, iChia-Ping, Taipei Tseng, iPo-Chih, Chiu, Yao-Ting, Siou-Shen, Cheng, Chih-Chi, Fang, Hung-Chi, Chao, Wei-Min, Chen and Liang-Gee 2006 A 5 mW MPEG4 SP encoder with 2D bandwidth sharing motion estimation for mobile applicationsiin Proc. ISSCCDig. Tech. Papers 1626–1635

- [13] Chaitanya, M.K. and Ravi, V., 2016. Design and development of BIST architecture for characterization of S-RAM stability. Indian Journal of Science and Technology, 9, p.21.

- [14] Ravi, V., and S. R. S. Prabaharan. "Memristor based memories: defects, testing, and testability techniques." Far East Journal of Electronics and Communications 17, no. 1 (2017): 105.

- [15] Sharma, A.K. and Ravi, V., 2017, March. A novel method for design and implementation of low power, high stable SRAM cell. In 2017 International Conference on Nextgen Electronic Technologies: Silicon to Software (ICNETS2) (pp. 112-116). IEEE.

- [16] iKursun V and iFriedman E G 2006 Multi-Voltage CMOS iCircuit Design

- [17] Wang A and Chandrakasan A 2005 A 180-mV subthreshold FFT processor using a minimum energy design methodology IEEE J. Solid-State Circuits 40 310–319

- [18] Patnaik, S. and Ravi, V., 2018. A built-in self-repair architecture for random access memories. In Nanoelectronic Materials and Devices (pp. 133-146). Springer, Singapore.

- [19] Sery G, Borkar S, and De V 2002 Life is CMOS: Why chase life after? in Proc. IEEE Des. Autom. Conf. 78–83