Received March 5, 2021, accepted April 2, 2021, date of publication April 7, 2021, date of current version April 22, 2021. *Digital Object Identifier* 10.1109/ACCESS.2021.3071538

# Implementation of Optimization-Based PI Controller Tuning for Non-Ideal Differential Boost Inverter

G. ARUNKUMAR<sup>®1</sup>, (Member, IEEE), DHANAMJAYULU C<sup>®1</sup>, (Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>®2</sup>, (Senior Member, IEEE), B RAJANARAYAN PRUSTY<sup>®1</sup>, (Senior Member, IEEE), AND BASEEM KHAN<sup>®3</sup>, (Member, IEEE)

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology (VIT), Vellore 632014, India

<sup>2</sup>CTIF Global Capsule (CGC) Laboratory, Department of Business Development and Technology, Aarhus University, 7400 Herning, Denmark

<sup>3</sup>Department of Electrical and Computer Engineering, Hawassa University, Hawassa 05, Ethiopia

Corresponding authors: G. Arunkumar (g.arunkumar@vit.ac.in) and Baseem Khan (baseem.khan04@gmail.com)

**ABSTRACT** The demand for renewable energy to sustain today's vulnerability towards depleting fossil fuels is a crucial agenda for research. Various inverter topologies have been proposed to convert renewable sources into a usable form. But output THD, additional filtering components at line frequency (leading to bulky circuitry), lower efficiency, etc., are some of the limitations faced in all those topologies. This paper aims to change a voltage source inverter's traditional behavior, which generates lesser output voltage with higher THD. The paper proposes a closed-loop non-ideal differential boost inverter (DBI) employing a PI controller. The optimization techniques such as, genetic algorithm (GA) and bacterial foraging optimization algorithm (BFOA) are incorporated to accentuate the PI controller's performance to produce a better response during line and load disturbance conditions with reduced THD. DBI performance is evaluated on a laboratory prototype with different loading conditions. A comparison between the algorithms and the previous topologies from the literature survey has also been provided to validate this research's claims. This paper's required simulation study is carried out using MATLAB, and real-time validation is carried out using dSPACE 1104 with sampling time of one  $\mu$ s.

**INDEX TERMS** Average modeling, bacterial foraging optimization algorithm (BFOA), differential boost inverter (DBI), genetic algorithm (GA), small signal modeling, tuning of PI controller.

# NOMENCLATURE

| R <sub>0</sub>                               | Load resistor                                 |  |  |  |  |

|----------------------------------------------|-----------------------------------------------|--|--|--|--|

| $S_1$ to $S_4$                               | Bidirectional IGBT switches                   |  |  |  |  |

| d,  â                                        | Large signal and small signal duty cycles     |  |  |  |  |

| D                                            | Steady-state duty cycle                       |  |  |  |  |

| $v_0, \hat{v}_0$                             | Large signal and small signal output voltages |  |  |  |  |

| $V_0$                                        | Steady-state output voltage                   |  |  |  |  |

| $V_{M}$                                      | Peak value of output voltage                  |  |  |  |  |

| $v_{\rm g}, \hat{v}_{\rm g}$                 | Large signal and small signal input voltages  |  |  |  |  |

| $V_{g}$                                      | Steady-state input voltage                    |  |  |  |  |

| ig                                           | Source current                                |  |  |  |  |

| $v_{C_1}, \hat{v}_{C_1}$                     | Large and small signal capacitor-1 voltages   |  |  |  |  |

| $V_{C_1}, V_{C_2}$                           | Steady-state capacitor-1 and capacitor-2      |  |  |  |  |

|                                              | voltages                                      |  |  |  |  |

| $v_{C_2}, \hat{v}_{C_2}$<br>$i_z, \hat{i}_z$ | Large and small signal capacitor-2 voltages   |  |  |  |  |

| $i_z, \hat{i}_z$                             | Large and small signal load currents          |  |  |  |  |

The associate editor coordinating the review of this manuscript and approving it for publication was Eklas Hossain<sup>(b)</sup>.

| $I_Z$                                     | Steady state load current                            |  |  |  |  |

|-------------------------------------------|------------------------------------------------------|--|--|--|--|

| $i_{L_1}, \hat{i}_{L_1}$                  | Large and small signal inductor-1 currents           |  |  |  |  |

| $I_{L_1}, I_{L_2}$                        | Steady state inductor-1 and inductor-2 cur-<br>rents |  |  |  |  |

| $i_{\mathrm{L}_2},\hat{i}_{\mathrm{L}_2}$ | Large and small signal inductor-2 currents           |  |  |  |  |

| $i_{C_1}, i_{C_2}$                        | Capacitor-1 and capacitor-2 currents                 |  |  |  |  |

| ron                                       | Resistance during on-time of switch                  |  |  |  |  |

| $r_{L_1}, r_{L_2}$                        | Internal resistances of high frequency inductors     |  |  |  |  |

| $k_{\rm P}, k_{\rm I}$                    | PI controller parameters                             |  |  |  |  |

| $t_{\rm r}, t_{\rm s}$                    | Rise time and settling time                          |  |  |  |  |

| P <sub>0</sub>                            | Peak overshoot                                       |  |  |  |  |

| E <sub>SS</sub>                           | Steady-state error                                   |  |  |  |  |

# I. INTRODUCTION

Inverters are a great addition to the power electronics world due to their ability to convert DC renewable sources' energy to AC usable form. Generally, the DC to AC

| Topology                                               | Ref.      | Power<br>rating<br>(W) | Input<br>voltage<br>(V) | Output<br>voltage<br>(V) | Voltage<br>gain | Switching<br>frequency<br>(kHz) | Control/<br>modulation<br>technique | No. of<br>active<br>devices | No. of<br>memory<br>elements | %<br>THD |

|--------------------------------------------------------|-----------|------------------------|-------------------------|--------------------------|-----------------|---------------------------------|-------------------------------------|-----------------------------|------------------------------|----------|

| Hybrid energy storage system                           | [1]       | 50                     | 24                      | 60                       | 2.5             | 20                              | SMC                                 | 8                           | 8                            | -        |

| Grid-connected fuel cell system                        | [5], [6]  | 1000                   | 42                      | 220                      | 5.23            | 20                              | DLC                                 | 7                           | 9                            | 4        |

| Active buck-boost inverter                             | [2]       | 500                    | 100 –<br>200            | 110                      | 0.55-<br>1.1    | 20                              | SPWM                                | 8                           | 2                            | -        |

| Boost inverter                                         | [7]       | 1000                   | 50                      | 220                      | 4.4             | 20                              | DLC                                 | 4                           | 4                            | 5.70     |

| DBI                                                    | [8]       | 44                     | 25                      | 42                       | 1.68            | 50                              | DLM                                 | 4                           | 4                            | 6.29     |

| Inverse Watkins-Johnson                                | [9]       | -                      | 53                      | 140                      | 2.6             | 10                              | SPWM                                | 6                           | 4                            | -        |

| Switched-capacitor DBI                                 | [10]      | 250                    | 60                      | 325                      | 5.4             | 50                              | SPWM                                | 8                           | 6                            | 6.1      |

| Single-stage sine-wave inverter                        | [11]      | 4.84                   | 16                      | 22                       | 1.375           | 10                              | SPWM                                | 4                           | 4                            | 10.80    |

| Boost inverter                                         | [3], [12] | 270                    | 96                      | 180                      | 1.875           | 20                              | SMC                                 | 4                           | 4                            | -        |

| Boost inverter                                         | [13]      | 175                    | 55                      | 270                      | 4.9             | 20                              | VMC                                 | 4                           | 4                            | 2.35     |

| GA-based tuning of PI controller<br>for boost inverter | [14]      | 220                    | 60                      | 311                      | 5.18            | 20                              | VMC                                 | 4                           | 4                            | 2.97     |

| BFOA-based tuning of PI controller for boost inverter  | [15]      | 55                     | 36                      | 155                      | 4.3             | 20                              | VMC                                 | 4                           | 4                            | 4.22     |

### TABLE 1. State-of-the-art in boost inverter.

boost converters can be broadly classified into three categories: (i) single-phase grid-connected battery-super capacitor hybrid energy storage system [1], (ii) active buck-boost full-bridge inverter [2], and (iii) boost-inverter [3]. Here the main challenges faced lie in the development of a low-cost, high-efficiency, high gain, and low THD topology, with small size power conversion system. On this note, the use of a differential boost inverter (DBI) is of choice. A DBI topology employs a single-stage power conversion from DC to AC. It uses differential boost converters, which are being controlled by two positive DC biased clamping sinusoidal references which are out of phase-shifted. The differences in the output of the converters produce an AC output voltage [3]. The possibility of generating higher AC output voltage from a comparatively lower input DC voltage, employing a single power conversion stage, is advantageous.

The DBI topology used in the literature comprises four ports (two power ports and two signal ports) [4]. The unregulated input and the regulated output represent two power ports, whereas the controlled input (duty cycle) and the sensed feedback signals represent two signal ports. TABLE 1 summarizes various attributes of DBIs, such as control strategies, modulation techniques, switching frequencies, etc. It is to mention here that the topologies compared in the table have different voltage, power ratings and are used for various applications. Further, the control technique employed uses many control parameters and feedback, leading to complexity in design. The use of diversifying control techniques in those studies is mainly because of their applications. The voltage mode control (VMC) technique is simple and well established whereas, the other control techniques such as sliding mode control (SMC) and double loop control (DLC) are primarily appreciated for their control mechanism's added flexibility. But, they have some lacunae. The SMC [1], [3], [12] and DLC [5], [6], [7] techniques require a minimum of four feedbacks for a fixed input voltage, and the number may further increase for the increase in feedback parameters as well as the multiple-input case. In [8], VMC and dynamic linearizing modulator (DLM) for DBI achieve stabilized output for a wide range of frequencies. Further, the feedbacks may drastically increase in number, or complexity may increase under the line and load disturbance conditions. A proper selection of the controller parameters in the case of VMC can tackle the issues described above. It is further to highlight that most of the above studies used the mathematical modeling of only one-half of the DBI, which indicates that the complete structure is not mathematically analyzed for the non-ideal case. As a result, the selection of controller parameters will be difficult under real-time disturbance conditions.

A close inspection on the DBI literature reveals that,

- (i) The use of mathematical models is only applied for a second-order system, i.e., for one-half of the DBI [4].

- (ii) A forth order mathematical modeling employed in [13], though accounts for non-ideal cases; stability analysis is not carried out.

- (iii) The topologies in [1], [3] [5]–[7], [10], [12] have employed intricate control strategies involving more control parameters leading to a bulky structure.

- (iv) An intuitive way of determining controller parameters by comparing multiple optimization algorithms has never been suggested in the literature.

Following the above research gaps in the literature, this research aims to provide a perfect DBI topology solution via mathematical modeling of the fourth-order non-ideal DBI system. The paper's significant contributions are listed underneath.

- (i) The controller parameters' selection is taken from the root locus plot, and the parameters' range values are confirmed from the stability region in the plot.

- (ii) The controller parameters are tuned in the confirmed stability region using optimization techniques, genetic algorithm (GA), and bacterial foraging optimization algorithm BFOA) to achieve a high-quality output sine wave with lower THD under line and load disturbances.

- (iii) The outcome is experimentally tested to be stable under the line and load disturbance conditions.

(iv) The obtained results under different voltage levels, power values, and load types using an experimental set-up attest to the proposed scheme's suitability for a real-time application.

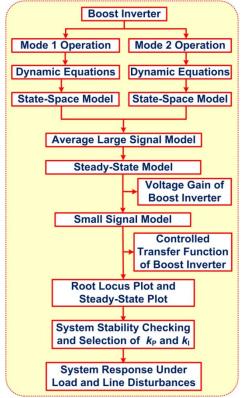

The research flowchart for the proposed topology of the non-ideal boost inverter scheme is elucidated in Fig. 1 for better clarity.

FIGURE 1. Research flow for the proposed work.

# **II. OPERATING MODES OF DBI**

# A. DESCRIPTION OF DBI

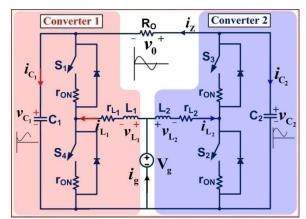

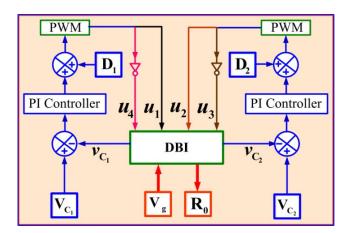

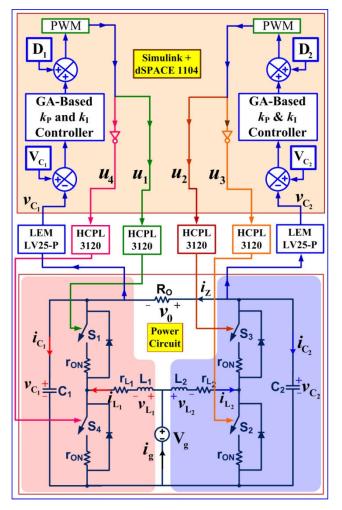

The DBI topology (refer to Fig. 2) consists of four IGBT switches, two high-frequency inductors, and two DC capacitors. The assumptions in modeling are: (i) use of non-ideal

FIGURE 2. Traditional DBI circuit for non-ideal case.

component, (ii) continuous converter current, (iii) inductance  $L_1 = L_2$ , and capacitance  $C_1 = C_2$ .

# **B. DBI OPERATIONAL MODES**

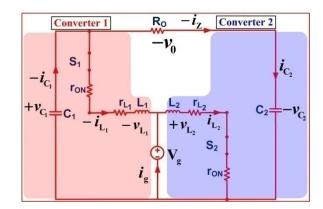

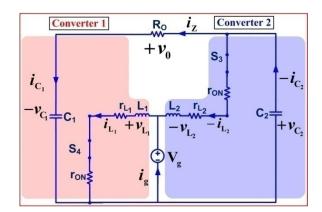

There are two modes of operation for the DBI, Mode 1, and Mode 2, which are respectively portrayed in Fig. 3 and Fig. 4. In each mode, two of the switches are in the on state and remaining in the off state.

FIGURE 3. Mode 1 operation (S<sub>1</sub> and S<sub>2</sub> are ON) of DBI.

FIGURE 4. Mode 2 operation (S<sub>3</sub> and S<sub>4</sub> are ON) of DBI.

Detailed dynamic equations and state-space models for the operational modes of the DBI can be found in [13]. From the state-space model, the average model is formed. The non-ideal state-space equations related to the average model, the steady-state model, the small-signal model, and the controlled transfer functions are as detailed under:

### 1) AVERAGE MODEL

The DBI's average state-space model [13] as derived from Fig. 3 and 4 is as follows.

$$\begin{bmatrix} \dot{i}_{L_1} \\ \dot{i}_{L_2} \\ \cdot \\ v_{C_1} \\ \cdot \\ v_{C_2} \end{bmatrix} = \begin{bmatrix} -r/L_1 & 0 & -d/L_1 & 0 \\ 0 & -r/L_2 & 0 & (d-1)/L_2 \\ d/C_1 & 0 & -1/RC_1 & 1/RC_1 \\ 0 & (1-d)/C_2 & 1/RC_2 & -1/RC_2 \end{bmatrix}$$

$$\times \begin{bmatrix} i_{L_1} \\ i_{L_2} \\ v_{C_1} \\ v_{C_2} \end{bmatrix} + \begin{bmatrix} 1/L_1 \\ 1/L_2 \\ 0 \\ 0 \end{bmatrix} \begin{bmatrix} v_g \end{bmatrix}$$

(1)

$$[v_{0}] = \begin{bmatrix} 0 \ 0 \ -1 \ 1 \end{bmatrix} \begin{bmatrix} i_{L_{1}} \\ i_{L_{2}} \\ v_{C_{1}} \\ v_{C_{2}} \end{bmatrix}$$

(2)

#### STEADY-STATE MODEL

By equating the differential terms to zero in (1), the resulting steady-state model help deriving the converter voltage gains and duty cycles as formulated under.

$$g_{1} = \frac{V_{C_{1}}}{V_{g}} = \frac{D^{3}R - 2D^{2}R + DR + r}{\left(D^{4} - 2D^{3} + D^{2}\right)R + \left(2D^{2} - 2D + 1\right)r}$$

(3)

$$D_{1} = \frac{\sqrt{(g_{1}^{2} - 2g_{1} + 1)R^{2} - 8g_{1}^{2}rR - (g_{1} + 1)R}}{2g_{1}R}$$

(4)

$$g_2 = \frac{V_{C_2}}{V_g} = \frac{-D^3 R - D^2 R + r}{(D^4 - 2D^3 + D^2) R + (2D^2 - 2D + 1) r}$$

(5)

$$D_{2} = \frac{\sqrt{(g_{2}^{2} - 2g_{2} + 1)R^{2} - 8g_{2}^{2}rR - (g_{2} - 1)R}}{2g_{2}R}$$

(6)

The voltage gain of the DBI can be obtained as the difference of the voltage gains " $g_2$ " and " $g_1$ " as in (3) and (5), respectively. Further, the ideal voltage gains and duty cycles can easily be obtained by substituting the value of "r" set to zero in (3) through (6).

## 3) SMALL-SIGNAL MODEL

The DBI circuit in Fig. 2 comprises non-linear switches. To control DBI during line and load disturbance cases, it must operate the voltage gain in the linear region where a small elemental length helps tune the output voltage with respect to the duty cycle. On this note, an establishment of a smallsignal model is vital.

$$\begin{bmatrix} \bullet \\ i_{L_{1}} \\ \bullet \\ i_{L_{2}} \\ \bullet \\ v_{C_{1}} \\ \bullet \\ v_{C_{2}} \end{bmatrix} = \begin{bmatrix} -r/L_{1} & 0 & -D/L_{1} & 0 \\ 0 & -r/L_{2} & 0 & (D-1)/L_{2} \\ D/C_{1} & 0 & -1/RC_{1} & 1/RC_{1} \\ 0 & (1-D)/C_{2} & 1/RC_{2} & -1/RC_{2} \end{bmatrix} \\ \times \begin{bmatrix} \wedge \\ i_{L_{1}} \\ i_{L_{2}} \\ \wedge \\ v_{C_{2}} \end{bmatrix} + \begin{bmatrix} 1/L_{1} & -VC_{1}/L_{1} \\ 1/L_{2} & -VC_{2}/L_{2} \\ 0 & -IL_{1}/C_{1} \\ 0 & -IL_{2}/C_{2} \end{bmatrix} \begin{bmatrix} \wedge \\ v_{g} \\ h \end{bmatrix}$$

(7)

FIGURE 5. Root locus plot of closed-loop DBI.

$$\begin{bmatrix} \uparrow \\ v_O \end{bmatrix} = \begin{bmatrix} 0 \ 0 \ -1 \ 1 \end{bmatrix} \begin{bmatrix} \uparrow \\ i_{L_1} \\ \uparrow \\ i_{L_2} \\ \uparrow \\ v_{C_1} \\ \uparrow \\ v_{C_2} \end{bmatrix}$$

(8)

#### 4) CONTROLLED TRANSFER FUNCTION

The controlled transfer function as the ratio between  $\hat{v}_0$  (in (8)) and  $\hat{d}$  (in (7)) is given in (9). The detailed formulation can be found in Appendix.

$$H(s) = \frac{\hat{v}_O(s)}{\hat{d}(s)} \tag{9}$$

#### **III. OPTIMIZATION OF PI CONTROLLER PARAMETERS**

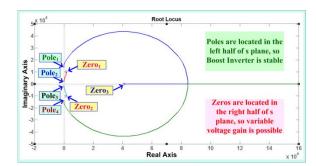

The closed-loop controlled transfer function model of DBI has three zeros and four poles, located respectively in the RHS and LHS of the s-plane (refer to Fig. 5), demonstrating the non-minimum phase characteristic [16]. Such a feature helps get a variable output voltage on the load side. The selection of controller parameters from the Root Locus plot is detailed underneath.

$$k = k_{\rm P} + \frac{k_{\rm I}}{s} \Rightarrow k = k_{\rm P} \left(\frac{s+a}{a}\right),$$

(10)

where,

$$a = \frac{k_{\rm I}}{k_{\rm P}}.\tag{11}$$

#### A. CLOSED LOOP DBI

The closed loop DBI block diagram is shown in Fig. 6. The converter 1 switches  $S_1$  and  $S_4$  (refer to Fig. 2) are turned on by control inputs  $u_1$  and  $u_4$  respectively. Similarly, the converter 2 switches  $S_2$  and  $S_3$  (refer Fig. 2) are triggered respectively by control inputs  $u_2$  and  $u_3$ . The output voltage is controlled by VMC technique. The reference voltages for the converters are expressed as,

$$V_{C_2} = V_{DC} + \left(\frac{V_M}{2}\right) \sin\theta, \qquad (12)$$

$$V_{C_1} = V_{DC} + \left(\frac{V_M}{2}\right) \sin\left(\theta - 180^0\right), \qquad (13)$$

VOLUME 9, 2021

FIGURE 6. Block diagram of closed-loop DBI for non-ideal case.

where the DC component,  $V_{DC} > V_g + \left(\frac{V_M}{2}\right)$  help obtain a perfect sinusoidal output voltage waveform.

Finally, the output voltage is obtained as difference of (12) and (13) and can be expressed as,

$$V_0 = V_{C_2} - V_{C_1} = V_M \sin \theta.$$

(14)

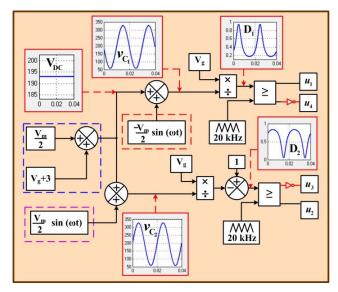

For an easy understanding, the closed-loop duty cycle generation technique is detailed in Fig. 7 for an ideal case. A double edge carrier PWM technique has been employed to obtain the duty cycle for the DBI.

FIGURE 7. SPWM implementation using double edge carrier wave.

For real-time implementation of the closed loop non-ideal DBI, (3)-(6) are used for the steady-state voltage gain and duty cycle generation.

# B. GA-BASED TUNING OF PI CONTROLLER

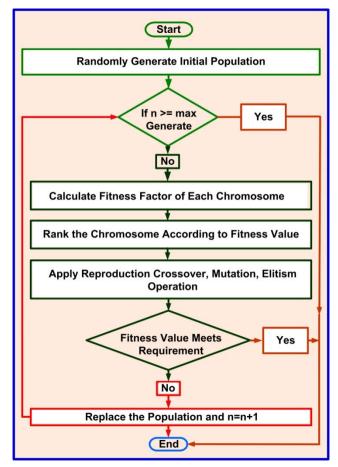

This control strategy is based on "survival of the fittest." It aims to eliminate the weakest members from a gene pool, resulting in a more robust future generation. This strategy

has been previously applied on a novel boost DC-DC converter [17] and a buck-boost feedback controller design [10]. It is also used in reducing harmonic contents in a multilevel converter [16]. The design flow of the GA is explained in Fig. 8.

FIGURE 8. Generalized GA-based design flow for parameter tuning.

Here, the objective is to accomplish rapid turn on and turn off, i.e., by minimizing the values of transient parameters  $t_r$ ,  $t_s$ , P<sub>0</sub>, and E<sub>SS</sub> [17]. On this note, a GA-based optimization is carried out with the following parameter specifications:

(i) Population size of 75,

(ii) Chromosome structure is binary coding, and

(iii) Reproduction is probabilistic crossover followed by mutation. Multi-point crossover is applied with ten iterations. The objective function is given as,

$$\operatorname{Min} F = (1 + t_{\rm r}) \left( 1 + t_{\rm s} \right) \left( 1 + {\rm P}_0 \right) \left( 1 + {\rm E}_{\rm SS} \right), \tag{15}$$

subjected to,  $\varphi_{\text{(Lower)}} \leq \varphi \leq \varphi_{\text{(Upper)}}$ , where  $\varphi = \{k_{\text{P}}, k_{\text{I}}\}$ .

The range of values of  $k_P$  and  $k_I$  to be used as upper and lower limits in the GA, are taken from the root locus plot (refer Fig. 5) and are listed down.

$$k_{\rm P}$$

(Min) = 0.000001, and  $k_{\rm P}$  (Max) = 0.0001

$k_{\rm I}$  (Min) = 0.0000001, and  $k_{\rm I}$  (Max) = 0.00001

The final values of  $k_{\rm P}$  and  $k_{\rm I}$  are found to be 0.00003 and 0.000008 respectively which are obtained through GA-based tuning (performed using MATLAB) to stabilize the DBI output voltage. Fig. 9 shows the control strategy involved in the GA-based tuning of the PI controller for the rapid prototype control of DBI using dSPACE 1104.

**FIGURE 9.** Block diagram of GA-based tuning of the PI controller used for the closed-loop DBI.

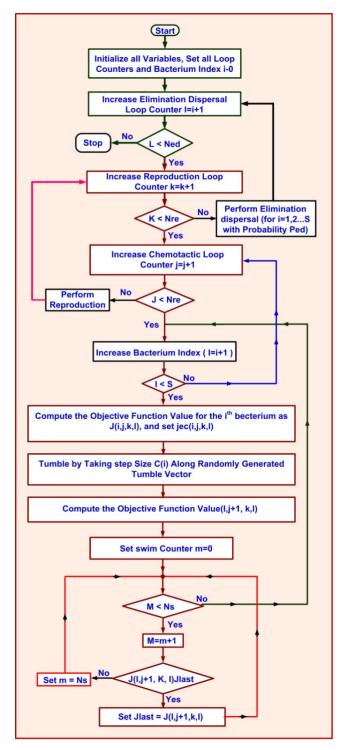

## C. BFOA BASED TUNING OF PI CONTROLLER

The BFOA is based on the strategy of "elimination and dispersal." While foraging, a bacterium tries to garner maximum energy while searching for nutrients and communicates with other bacteria. It essentially follows a chemotactic movement while solving a problem utilized in this algorithm [18]. The block diagram of the BFOA-based tuning of the PI controller to control the DBI is shown in Fig. 10. The flow of the BFOA control strategy is similar to that of Fig. 9 but by replacing both the blocks namely "GA-Based  $k_P$  and  $k_I$  Controller" by "BFOA-Based  $k_P$  and  $k_I$  Controller". It is to mention that, the parameter tuning process using BFOA (as discussed in Fig. 10) is more involved as compared to GA-based design flow as discussed in Fig. 8. This leads to more computational

FIGURE 10. Generalized BFOA-based design flow for parameter tuning.

time compared to GA-based tuning. The strategy is utilized to tune the PI controller, which in turn controls the DBI. The dotted boundary box in the figure refers to the complete control unit functioning with MATLAB and dSPACE 1104. The voltage sensor output acts as the sensing voltage (for duty cycle calculation) through dSPACE 1104 analog ports.

The PWM signal is collected from the slave I/O port in the dSPACE. The population size and the number of iterations are ten. The chemotactic size and the reproductive loop size are four, the elimination and dispersal loop size is two, the swim length is four, and the dispersal probability is 0.2. The objective function and constraint are the same as in (15).

## **IV. RESULTS AND DISCUSSIONS**

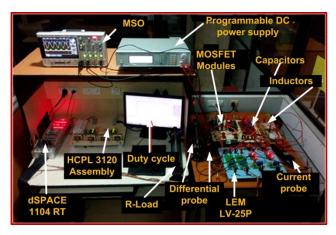

This Section consists of four subsections to help manifest and validate the paper's purpose claimed so far. The first one discusses the traditionally controlled DBI employing a PI controller. Different voltage rating results have been showcased as stages. Stage 1 is performed at low voltage levels to observe the converter's behavior in the event of disturbances. In stage 2, results depict standard 220 V operations. The detailed analysis of GA and the BFOA-based tuning of the PI controller for better results are elucidated respectively in subsections IV (B) and IV (C). Hardware results implementing the algorithms are also given in these two subsections. Finally, the fourth subsection compares the THD results obtained by employing the algorithms and their influence on producing a better output from the DBI. A detailed comparison between the traditional topologies in the literature survey and the proposed topology has been provided. The required simulation is carried out using MATLAB-Simulink. The hardware setup for validating the closed-loop DBI claimed in this model is shown in Fig. 11.

FIGURE 11. Hardware setup of DBI using dSPACE 1104.

# A. NON-IDEAL DBI EMPLOYING A PI CONTROLLER

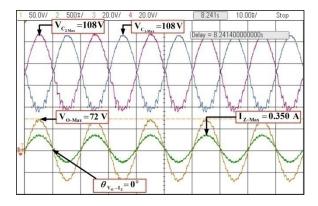

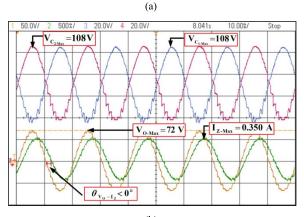

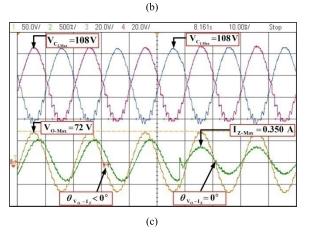

TABLE 2 shows the stage 1 design parameters used to determine the DBI's performance with resistive and motor load under various load combinations. The relevant results are also provided in Fig. 12 (a)-(c). The expected phase shift as obtained in Fig. 12 (a) and (b) indicates the DBI's smooth performance under boosted gain. Further, in Fig. 12 (c), it is noteworthy that the load voltage is stable under load disturbance conditions. TABLE 3 shows the design parameters for the stage 2 result analysis. Fig. 13 (a) depicts the hardware results obtained for the DBI under study. The obtained AC

#### VOLUME 9, 2021

#### TABLE 2. Stage 1 specifications.

| Parameter                                    | Value             |

|----------------------------------------------|-------------------|

| Input DC voltage, V <sub>g</sub>             | 24 V              |

| Output AC voltage, V <sub>o</sub>            | 72 V (Max. value) |

| Reference sine wave frequency                | 50 Hz             |

| Switching frequency, f <sub>s</sub>          | 20 kHz            |

| Inductors, $L_1$ and $L_2$                   | 500 μΗ            |

| Parasitic resistance in series with inductor | 0.1 Ω             |

| Capacitors, $C_1$ and $C_2$                  | 20 µF             |

| Dual IGBT modules, $S_1$ to $S_4$            | CM75DU-12H        |

| Switch on-time resistance                    | 1 mΩ              |

| Load resistor, R                             | 220 Ω             |

| Universal motor load rating                  | 220 V             |

| Real-time interfacing kit                    | dSpace-1104       |

| Voltage sensor, LEM LV 25-P                  | 500 V             |

#### TABLE 3. Stage 2 specifications.

| Parameter                                    | Value              |

|----------------------------------------------|--------------------|

| Input DC voltage, V <sub>g</sub>             | 48 V               |

| Output AC voltage, V <sub>o</sub>            | 308 V (Max. value) |

| Reference sine wave frequency                | 50 Hz              |

| Switching frequency, f <sub>s</sub>          | 20 kHz             |

| Inductors, $L_1$ and $L_2$                   | 700 µH             |

| Parasitic resistance in series with inductor | 0.1 Ω              |

| Capacitors, $C_1$ and $C_2$                  | 10 µF              |

| Dual IGBT modules, $S_1$ to $S_4$            | CM75DU-12H         |

| Switch on-time resistance                    | 1 mΩ               |

| Load resistor, R                             | 220 Ω              |

| Real-time interfacing kit                    | dSpace-1104        |

| Voltage sensor, LEM LV 25-P                  | 500 V              |

RMS output voltage is almost equal to 220V. Finally, the THD value is indicated in Fig. 13 (b).

# B. GA-BASED TUNING OF PI CONTROLLER

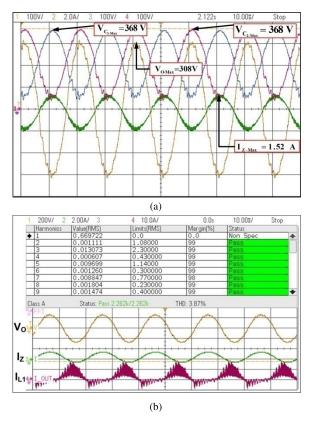

The GA-based closed loop DBI (refer to Fig. 9) is successfully implemented in Fig. 11. The design parameters involved in the GA-based tuning of the PI controller used for DBI is presented in TABLE 4. The hardware result for the resistive load is shown in Fig. 14 (a), whereas for the motor load, it is given in Fig. 14 (b). Fig. 14 (c) shows that even under load disturbance, the system's output voltage regains its stability within one cycle. Fig 14 (d) indicates that the output voltage of DBI reached the steady-state in less than a cycle under input transient condition.

The input voltage is rapidly changed from 0 V to the rated value to incorporate a transient environment. Even then, the output voltage attains stability in a cycle, and this proves the claim of improved settling time due to the usage of the GA

FIGURE 12. Stage 1 steady-state testing with (a) Resistive load, (b) Motor load, (c) Load disturbance test.

algorithm. Even when the line disturbance was introduced the integral and proportional constants generated by the GA algorithm forced the response to become stable as shown in Fig. 14 (e). The THD result obtained after tuning the PI controller of the DBI with GA is given in Fig. 14 (f).

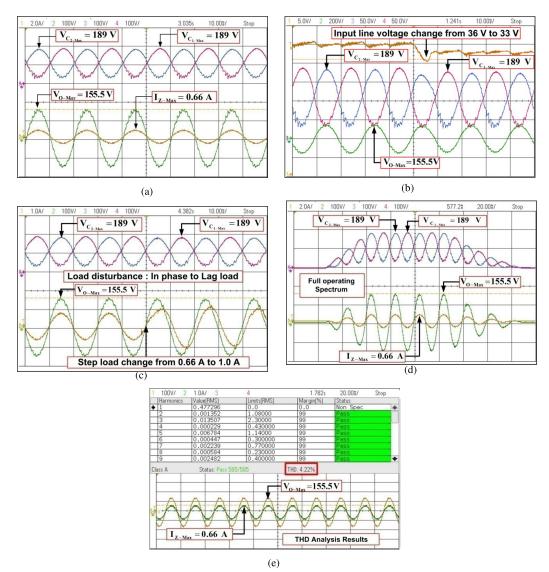

## C. BFOA -BASED TUNING OF PI CONTROLLER

The design parameter for the BFOA-based PI controller for the DBI is provided in TABLE 5.

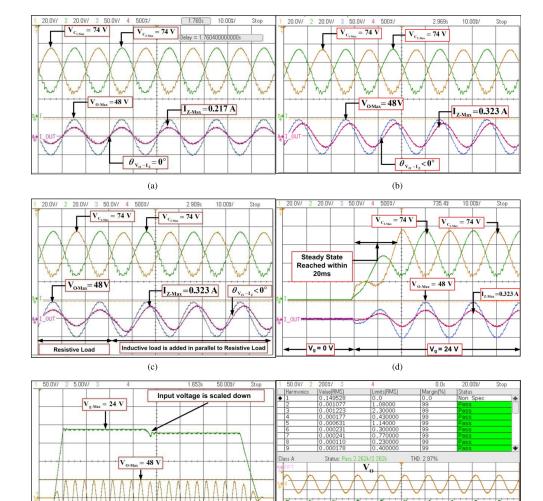

Fig. 15 (a) results showcase the steady-state capacitor voltages along with the output current and voltage wave-forms. Fig. 15 (b) shows line disturbance response. Even after

FIGURE 13. (a) V<sub>0</sub>, V<sub>C1</sub>, V<sub>C2</sub> and I<sub>Z</sub> as obtained from the DBI, (b) Graph of steady-state results of V<sub>0</sub>, I<sub>Z</sub>, and I<sub>L1</sub> during stage 2 operation.

TABLE 4. Specifications for GA-based PI controlled DBI.

| Parameter                                    | Value               |

|----------------------------------------------|---------------------|

| Input DC voltage, V <sub>g</sub>             | 24 V                |

| Output AC voltage, V <sub>o</sub>            | 48 V (Max. value)   |

| Reference sine wave frequency                | 50 Hz               |

| Switching frequency, f <sub>s</sub>          | 20 kHz              |

| Inductors, $L_1$ and $L_2$                   | 500 µH              |

| Parasitic resistance in series with inductor | 0.1 Ω               |

| Capacitors, $C_1$ and $C_2$                  | 20 µF               |

| Dual IGBT modules, $S_1$ to $S_4$            | CM75DU-12H          |

| Switch on-time resistance                    | $1 \text{ m}\Omega$ |

| Load resistor, R                             | 220 Ω               |

| Universal motor load rating                  | 220 V               |

| Real time interfacing kit                    | dSpace-1104         |

| Voltage sensor, LEM LV 25-P                  | 500 V               |

incorporating the line disturbance, due to the stepping down of the input voltage from 36 V to 33 V (line disturbance), the current waveform stabilizes in just 20 ms due to BFOA controlling in the PI controller. In Fig. 15 (c), load disturbance is depicted by a sudden load change from a unity power factor to a lagging power factor, which has negligible

(c) (f) FIGURE 14. GA-based DBI steady-state response for (a) Resistive load, (b) Motor load, (c) Load disturbance, (d) Transient response, (e) Supply voltage regulation and transience, (f) THD results for resistive load.

TABLE 5. Specifications for BFOA-based PI controlled DBI.

20 ms

| Parameter                                    | Value                |

|----------------------------------------------|----------------------|

| Input DC voltage, Vg                         | 36 V                 |

| Output AC voltage, V <sub>o</sub>            | 155.5 V (Max. value) |

| Reference sine wave frequency                | 50 Hz                |

| Switching frequency, fs                      | 20 kHz               |

| Inductors, $L_1$ and $L_2$                   | 200 µH               |

| Parasitic resistance in series with inductor | 0.1 Ω                |

| Capacitors, $C_1$ and $C_2$                  | 20 µF                |

| Dual IGBT modules, S1 to S4                  | CM75DU-12H           |

| Switch on-time resistance                    | $1 \text{ m}\Omega$  |

| Load resistor, R                             | 220 Ω                |

| Universal motor load rating                  | 220 V                |

| Real time interfacing kit                    | dSpace-1104          |

| Voltage sensor, LEM LV 25-P                  | 500 V                |

System is stable

influence on the voltage waveform. In contrast, the current waveform attains stability again in just 20 ms indicating the advantage of using the BFOA technique to control the PI

VOLUME 9, 2021

TABLE 6.

System response for traditional PI, GA-based PI and BFOA-based PI.

| Dynamic<br>response<br>specifications | $\begin{array}{ccc} & \text{Traditional} & \text{GA} \\ & \text{method} & (k_{\rm P} = 0.00023, \\ k_1 = 0.000001, & k_1 = 0.000008) \end{array}$ |         | BFOA<br>$(k_{\rm P} = 0.000053, k_{\rm I} = 0.000009)$ |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------|--|--|

| t <sub>r</sub>                        | 5.61 ms                                                                                                                                           | 5.62 ms | 5.5 ms                                                 |  |  |

| ts                                    | 18.5 ms                                                                                                                                           | 17 ms   | 16.9 ms                                                |  |  |

| $\mathbf{P}_0$                        | 0                                                                                                                                                 | 0       | 0                                                      |  |  |

| Ess                                   | 0.513 V                                                                                                                                           | 0.414 V | 0.402 V                                                |  |  |

controller used in the DBI. Even during turn on and turn off, the waveforms attained are smooth and within the desirable range, as depicted by Fig. 15 (d). THD response is shown in Fig. 15 (e).

# D. FURTHER DISCUSSIONS AND COMPARISONS

As manifested by the hardware results, a DC to AC conversion was achieved. A close-loop circuit was implemented

FIGURE 15. (a) Capacitor voltages, Output current and output voltages obtained in the steady-state, (b) Line disturbance response, (c) Load disturbance response, (d) Transient response during turn on and turn off, (e) THD analysis.

successfully, and the performance was enhanced by incorporating the GA and BFOA algorithms. A better response was obtained by reducing the rise time, settling time, maximum overshoot, and the steady-state error, as shown in TABLE 6. The THD values were less than 5% which complies with Class-A IEEE standard 519-2014. Also, the response during line and load disturbances reached a steady state in significantly less time. Thus, the result complies with the claims made at the beginning of this research.

## **V. CONCLUSION**

The voltage gain and the THD results so obtained comply with the claims made at the beginning of this research. The modeling of the proposed DBI is done for the non-ideal case, thus, providing the expected result. Despite the incorporation of load disturbance, the output waveforms attain stability in just one cycle due to the GA and BFOA algorithms' addition to tune the PI controller. A detailed benefit of this addition has been highlighted. Also, in stages, hardware results for different ratings have been given to prove the versatile applications in which this inverter can be used. A future prospectus for this topology would be to extend it as a three-phase inverter to cater to the higher power demands used in industrial devices.

## APPENDIX

# FORMULATION OF CONTROLLED TRANSFER FUNCTION

The transfer function in (9) can be derived as,

$$\frac{\hat{v}_O(s)}{\hat{d}(s)} = \frac{(q_1x_4 + q_2x_3 + q_3x_2 + q_4x_1)}{s^4 + n_1s^3 + n_2s^2 + n_3s + n_4}$$

where,

$$q_{1} = -s^{3} - m_{20}s^{2} + m_{17}s - m_{21}s + m_{18}s - m_{22} + m_{19}$$

$$q_{2} = s^{3} - m_{14}s^{2} + m_{11}s^{2} - m_{15}s + m_{12}s - m_{16} + m_{13}$$

$$q_{3} = -m_{8}s^{2} - m_{9}s + m_{7} - m_{10}$$

$$q_{4} = m_{1}s^{2} - m_{4}s + m_{2}s - m_{5} + m_{3}$$

$$n_{1} = -k_{6} - k_{3} + k_{10} - k_{1}$$

$$n_{2} = -k_{7}k_{9} - k_{4}k_{8} + (k_{3} + k_{10} + k_{1})k_{6} - k_{2}k_{5}$$

$$+ (k_{10} + k_{1})k_{3} + k_{1}k_{10}$$

$$n_{3} = (k_{3} + k_{1})k_{7}k_{9} + (k_{4}k_{6} + k_{1}k_{4})k_{8}$$

$$+ ((-k_{10} - k_{1})k_{3} - k_{1}k_{10})k_{6}$$

$$+ (k_{2}k_{3} + k_{10}k_{2})k_{5} - k_{1}k_{10}k_{3}$$

$$n_{4} = k_{1}k_{3}k_{7}k_{9} + (k_{2}k_{4}k_{5} - k_{1}k_{4}k_{6})k_{8}$$

$$+ k_{1}k_{10}k_{3}k_{6} - k_{10}k_{2}k_{3}k_{5}$$

$$m_{1} = k_{5}, m_{2} = (-k_{3} - k_{10})k_{5}, m_{3} = -k_{4}k_{5}k_{8} + k_{10}k_{3}k_{5}$$

$$m_{4} = k_{5}k_{9}, m_{5} = -k_{3}k_{5}k_{9}, m_{6} = k_{7}k_{8}, m_{7} = -k_{1}k_{7}k_{8}$$

$$m_{8} = k_{8}, m_{9} = -k_{6}k_{1}k_{8}, m_{10} = (k_{6}k_{1} - k_{2}k_{5})k_{8}$$

$$m_{11} = -k_{3} - k_{10} - k_{1},$$

$$m_{12} = -k_{4}k_{8} + (k_{10} + k_{1})k_{3} + k_{1}k_{10}$$

$$m_{13} = k_{1}k_{8} - k_{1}k_{10}k_{3}, m_{14} = k_{9}, m_{15} = (-k_{3} - k_{1})k_{9}$$

$$m_{16} = k_{1}k_{3}k_{9}, m_{17} = k_{7}, m_{18} = (-k_{3} - k_{1})k_{7}$$

$$m_{19} = k_{1}k_{3}k_{7}, m_{20} = -k_{6} - k_{3} - k_{1}$$

$$m_{21} = (k_{1} + k_{3})k_{6} - k_{2}k_{5} + k_{1}k_{3},$$

$$m_{22} = -k_{1}k_{3}k_{6} + k_{2}k_{3}k_{5}$$

$$k_{1} = -r/L_{1}, k_{2} = -D/L_{1}, k_{3} = -r/L_{2}, k_{4} = (D-1)/L_{2},$$

$$k_{5} = d/C_{1}, k_{6} = -1/RC_{1}, k_{7} = 1/RC_{1}, k_{8} = (1-D)/C_{2},$$

$$k_{9} = 1/RC_{2}, k_{10} = -1/RC_{2}, x_{1} = -VC_{1}/L_{1},$$

$$x_{2} = VC_{2}/L_{2},$$

$$x_{3} = IL_{1}/C_{1}, x_{4} = -IL_{2}/C_{2}$$

#### REFERENCES

- [1] D. B. W. Abeywardana, B. Hredzak, and V. G. Agelidis, "A fixed-frequency sliding mode controller for a boost-inverter-based battery-supercapacitor hybrid energy storage system," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 668–680, Jan. 2017.

- [2] Y. Tang, X. Dong, and Y. He, "Active buck-boost inverter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4691–4697, Sep. 2014.

- [3] R. Caceres and I. Barbi, "A boost DC-AC converter: Operation, analysis, control and experimentation," in *Proc. IECON-21st Annu. Conf. IEEE Ind. Electron.*, Orlando, FL, USA, vol. 1, Nov. 1995, pp. 546–551.

- [4] R. O. Caceres and I. Barbi, "A boost DC-AC converter: Analysis, design, and experimentation," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 134–141, Jan. 1999.

- [5] M. Jang and V. G. Agelidis, "A minimum power-processing-stage fuel-cell energy system based on a boost-inverter with a bidirectional backup battery storage," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1568–1577, May 2011.

- [6] M. Jang, M. Ciobotaru, and V. G. Agelidis, "A single-phase grid-connected fuel cell system based on a boost-inverter," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 279–288, Jan. 2013.

- [7] O. J. Moraka, P. S. Barendse, and M. A. Khan, "Dead time effect on the double-loop control strategy for a boost inverter," *IEEE Trans. Ind. Appl.*, vol. 53, no. 1, pp. 319–326, Jan. 2017.

- [8] K. Jha, S. Mishra, and A. Joshi, "High-quality sine wave generation using a differential boost inverter at higher operating frequency," *IEEE Trans. Ind. Appl.*, vol. 51, no. 1, pp. 373–384, Jan. 2015.

- [9] S. Mishra, R. Adda, and A. Joshi, "Inverse Watkins–Johnson topology-based inverter," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1066–1070, Mar. 2012.

- [10] G. V. Silva, J. M. D. Andrade, R. F. Coelho, and T. B. Lazzarin, "Switched-capacitor differential boost inverter: Design, modeling, and control," *IEEE Trans. Ind. Electron.*, vol. 67, no. 7, pp. 5421–5431, Jul. 2020.

- [11] G. S. Ilango, P. S. Rao, A. Karthikeyan, and C. Nagamani, "Singlestage sine-wave inverter for an autonomous operation of solar photovoltaic energy conversion system," *Renew. Energy*, vol. 35, no. 1, pp. 275–282, Jan. 2010.

- [12] R. Caceres and I. Barbi, "Sliding mode controller for the boost inverter," in *Proc. 5th IEEE Int. Power Electron. Congr. Tech.*, Cuernavaca, Mexico, Oct. 1996, pp. 247–252.

- [13] G. Arunkumar and I. Gnanambal, "Modeling of boost inverter," Int. J. Appl. Eng. Res., vol. 10, no. 16, pp. 36128–36133, 2015.

- [14] G. Arunkumar, I. Gnanambal, and S. Naresh, "Boost inverter: A new proportional integral control strategy for resistive and motor loads using genetic algorithm," *Int. J. Appl. Eng. Res.*, vol. 10, no. 16, pp. 36122–36127, 2015.

- [15] G. Arunkumar and D. I. Gnanambal, "Utilization of bacterial foraging algorithm for optimization of boost inverter parameters," *Circuits Syst.*, vol. 7, no. 8, pp. 1430–1440, 2016.

- [16] B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "Harmonic optimization of multilevel converters using genetic algorithms," *IEEE Power Electron Lett.*, vol. 3, no. 3, pp. 92–95, Sep. 2005.

- [17] K. Sundareswaran, K. V. S. M. K. Vadali, S. K. Nadeem, and H. N. Shyam, "Robust controller identification for a boost type DC-DC converter using genetic algorithm," in *Proc. IEEE Region 3rd Int. Conf. Ind. Inf. Syst.*, Kharagpur, India, Dec. 2008, pp. 1–5.

- [18] K. Sundareswaran, V. Devi, S. Sankar, P. S. R. Nayak, and S. Peddapati, "Feedback controller design for a boost converter through evolutionary algorithms," *IET Power Electron.*, vol. 7, no. 4, pp. 903–913, Apr. 2014.

- [19] V. Sharma, S. Pattnaik, and T. Garg, "A review of bacterial foraging optimization and its applications," in *Proc. IEEE National Conf. Future Aspects Artif. Intell. Ind. Automat. (NCFAAIIA)*, New Delhi, India, Dec. 2012, pp. 9–12.

**G. ARUNKUMAR** (Member, IEEE) was born in Trichy, India, in 1979. He received the B.E. degree in electrical and electronics engineering from the University of Madras, India, in 2000, and the M.E. and Ph.D. degrees from Anna University, India, in 2005 and 2017, respectively. He is currently working as an Associate Professor with the School of Electrical Engineering, VIT, Vellore, India. His research interests include dc to dc converters, dc to ac PWM inverters, multilevel

inverters, boost inverters, grid-connected converters, grid-connected inverters, smart grid, electric vehicle, electric spring, and tuning of memory elements and controller parameters using soft-switching techniques for power converters, average modeling, steady-state modeling, small-signal modeling, and stability analysis of the converters and inverters.

**DHANAMJAYULU C** (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from JNTU University, Hyderabad, India, the M.Tech. degree in control and instrumentation systems from the Indian Institute of Technology Madras, Chennai, India, and the Ph.D. degree in power electronics from the Vellore Institute of Technology, Vellore, India. Since 2010, he has been a Senior Assistant Professor with the Vellore Institute of Technology. He was

invited as a Visiting Researcher with the Department of Energy Technology, Aalborg University, funded by the Danida Mobility Grant, Ministry of Foreign Affairs of Denmark on Denmark's International Development Cooperation. From 2019 to 2021, he was a Postdoctoral Fellow with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He is currently a Faculty Member and a member of the Control and Automation Department, School of Electrical Engineering, Vellore Institute of Technology. He is also a Senior Assistant Professor with the School of Electrical Engineering, Vellore Institute of Technology. His research interests include multilevel inverters, power converters, active power filters, power quality, grid-connected systems, smart grid, electric vehicle, electric spring, and tuning of memory elements and controller parameters using soft-switching techniques for power converters, average modeling, steady-state modeling, small-signal modeling, and stability analysis of the converters and inverters.

**SANJEEVIKUMAR PADMANABAN** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

From 2012 to 2013, he was an Associate Professor with VIT University. He joined the National Institute of Technology, India, as a Faculty Member, in 2013. He was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar,

in 2014, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. From 2016 to 2018, he worked as an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa. From March 2018 to February 2021, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. Since March 2021, he has been with the CTIF Global Capsule (CGC) Laboratory, Department of Business Development and Technology, Aarhus University, Herning, Denmark. He has authored over 300 scientific articles.

Dr. Padmanaban is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He was a recipient of the Best Paper cum Most Excellence Research Paper Award from IET-SEISCON'13, IET-CEAT'16, IEEE-EECSI'19, IEEE-CENCON'19, and five best paper awards from ETAEERE'16 sponsored Lecture Notes in Electrical Engineering, Springer book. He is an Editor/Associate Editor/Editorial Board for refereed journals, in particular the IEEE SystEMS JOURNAL, the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, IEEE AcCESS, *IET Power Electronics, IET Electronics Letters*, and the *International Transactions on Electrical Energy Systems*, a Subject Editorial Board Member of *Energy Sources— Energies Journal* (MDPI), and the Subject Editor of the *IET Renewable Power Generation, IET Generation, Transmission and Distribution*, and *FACTS* journal (Canada).

**B** RAJANARAYAN PRUSTY (Senior Member, IEEE) received the Ph.D. degree from the National Institute of Technology, Bengaluru. He is currently working as an Assistant Professor (Sr. Grade) with the School of Electrical Engineering, Vellore Institute of Technology, Vellore. In recognition of his research publications from 2017 to 2019, he was awarded the University Foundation Day Research Award-2019 from BPUT, Odisha, India. He has coauthored a textbook entitled *Power System Anal*-

*ysis: Operation and Control* in I. K. International Publishing House Pvt. Ltd. His research interests include time series preprocessing and forecasting, high-dimensional dependence modeling, and probabilistic power system analysis. He was a recipient of the prestigious POSOCO Power System Awards (PPSA) for the year 2019 under the doctoral category by Power System Operation Corporation Limited in partnership with FITT, IIT Delhi. Since 2015, he has been an Active Reviewer.

**BASEEM KHAN** (Member, IEEE) received the B.Eng. degree in electrical engineering from Rajiv Gandhi Technological University, Bhopal, India, in 2008, and the M.Tech. and D.Phil. degrees in electrical engineering from the Maulana Azad National Institute of Technology, Bhopal, in 2010 and 2014, respectively. He is currently working as a Faculty Member with Hawassa University, Ethiopia. His research interests include power system restructuring, power system plan-

ning, smart grid technologies, meta-heuristic optimization techniques, reliability analysis of renewable energy systems, power quality analysis, and renewable energy integration.