Contents lists available at ScienceDirect

Journal of Science: Advanced Materials and Devices

journal homepage: www.elsevier.com/locate/jsamd

**Original Article**

# Performance analysis of HfO<sub>2</sub>/InAlN/AlN/GaN HEMT with AlN buffer layer for high power microwave applications

ADVANCED

P. Murugapandiyan <sup>a, \*</sup>, A. Mohanbabu <sup>b</sup>, V. Rajya Lakshmi <sup>a</sup>, V.N. Ramakrishnan <sup>c</sup>, Arathy Varghese <sup>d</sup>, MOHD Wasim <sup>e</sup>, S. Baskaran <sup>f</sup>, R. Saravana Kumar <sup>g</sup>, V. Janakiraman <sup>h</sup>

<sup>a</sup> Department of Electronics and Communication Engineering, Anil Neerukonda Institute of Technology & Sciences, Visakhapatnam, India

<sup>b</sup> Department of Electronics and Communication Engineering, Karpagam College of Engineering, Coimbatore, India

<sup>c</sup> Department of Micro & Nanoelectronics, School of Electronics Engineering, VIT, Vellore, India

<sup>d</sup> Department of Department of Electrical Engineering, Indian Institute of Technology, Bombay, India

<sup>e</sup> Department of Electronics and Communication Engineering, Lovely Professional University, Jalandar, India

<sup>f</sup> Department of Electronics and Communication Engineering, SKP Engineering College, Thiruvannamalai, India

<sup>g</sup> Department of Electronics and Communication Engineering, Bannari Amman Institute of Technology, Sathyamangalam, India

h Department of Electronics and Communication Engineering, Dhanalakshmi Srinivasan College of Engineering and Technology, Mamallapuram, India

### ARTICLE INFO

Article history: Received 27 February 2020 Received in revised form 15 April 2020 Accepted 17 April 2020 Available online 26 April 2020

Keywords: MOS-HEMT HfO<sub>2</sub> JFoM Microwave applications Cut-off frequency Leakage current

### ABSTRACT

We present a performance enhancement evaluation of n + doped graded InGaN drain/source regionbased HfO<sub>2</sub>/InAlN/AlN/GaN/AlN on SiC metal-oxide-semiconductor high electron mobility transistor (MOS-HEMTs) with a T-shaped gate. Impact on the device characteristics with the inclusion of a HfO<sub>2</sub> surface passivation layer and an AlN buffer layer in the MOS-HEMT structure as a performance booster has been analyzed for the HEMT device with 30 nm gate length using Silvaco ATLAS TCAD. The proposed MOS-HEMT exhibits an outstanding performance, with an enhanced power gain cut-off frequency (f<sub>max</sub>) of 366 GHz, a current gain cut-off frequency (f<sub>t</sub>) of 426 GHz, and a off-state breakdown voltage (V<sub>br</sub>) of 81 V. The high-*k* (high permittivity) HfO<sub>2</sub> based metal oxide semiconductor HEMT device experiences a low off-state gate leakage current (I<sub>g</sub> ~ 10<sup>-11</sup>A/mm) and a high I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>9</sup>. The InAlN/GaN/AlN heterostructures demonstrate improved two-dimensional electron gas (2DEG ~ 5.3 × 10<sup>13</sup> cm<sup>-2</sup>), carrier mobility ( $\mu$ ) of 1256 Cm<sup>2</sup>/V-s and drain current density of (I<sub>ds</sub>) 2.7 A/mm. A large signal analysis performed at 30 GHz yielded a maximum of 28% power-added efficiency. The high JFoM of 34.506 THz V (Johnson Figure of Merit = f<sub>t</sub> × V<sub>br</sub>) and (f<sub>t</sub>.f<sub>max</sub>)<sup>1/2</sup> of 394.86 GHz indicate the potential applicability of the HfO<sub>2</sub>/InAlN/GaN MOS-HEMTs in high-frequency and high-power applications.

© 2020 The Authors. Publishing services by Elsevier B.V. on behalf of Vietnam National University, Hanoi. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/).

### 1. Introduction

III-Nitride based power transistors are attractive devices for millimetre-wave high-power and high-frequency applications. AlGaN/GaN-based high electron mobility transistors have demonstrated an outstanding power performance of 30 W/mm at 4 GHz [1]. Recent challenges in III-Nitride based HEMT are their poor operating frequencies in sub-millimeter wave frequencies for satellite, advanced radars, and broadband wireless communications. The realization of ultrathin-barrier based AlGaN/GaN heterostructures has remained a challenging task because of surface

E-mail address: murugavlsi@gmail.com (P. Murugapandiyan).

depletion effects [2] and physical damage in the recessed gate [3]. To achieve high frequency and high voltage operation of GaN-based HEMTs, a trade-off between current gain cut-off frequency ( $f_t$ ) and maximum oscillation frequency ( $f_{max}$ ) for breakdown voltage must be considered. In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN-based lattice-matched hetero-structures have demonstrated a stronger polarization, good thermal stability, and a high drain current density [4–6]. InAlN barrier based III-Nitride HEMT possessed cut-off frequencies ( $f_T$  and  $f_{max}$ ) of more than 300 GHz [7]. Ultra scaled InAlN barrier layer (3 nm) based HEMTs have shown an excellent thermal stability [8] and InAlN/GaN-based HEMTs reported in the last decade, reached a 5 W/mm output power at 35 GHz [9] and 40 GHz [10].

In spite of the remarkable improvement in the operating frequency, InAlN based HEMTs suffer from leakage currents and low breakdown voltage [11], severe short channel effects, and contact

Peer review under responsibility of Vietnam National University, Hanoi.

\* Corresponding author.

https://doi.org/10.1016/j.jsamd.2020.04.007

<sup>2468-2179/© 2020</sup> The Authors. Publishing services by Elsevier B.V. on behalf of Vietnam National University, Hanoi. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/).

resistances [12]. In particular, InAlN based HEMTs have shown high buffer leakage currents at high temperatures. InAlN/GaN HEMT on SiC substrate has shown the higher performance compared to HEMTs on other substrates. Despite the high-frequency performance of GaN-based HEMT demonstrated in refs [13,14], the devices experienced severe short channel effects and gate leakage current for the sub-50 nm gate length. Several research groups have investigated metal oxide semiconductors high electron mobility transistors (MOS-HEMTs) using various oxide layers such as SiO2, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, MgCaO and La<sub>2</sub>O<sub>3</sub> for improving the device performance by suppressing gate leakage currents [15–22].

At high drain bias, the device performance gets degraded from its dynamic on-resistance, also known as current collapse and surface traps, which act as a "virtual gate" in the gate to drain access region. This prevents a proper operation of the device and reduces the available current swing as well as degrades the knee voltage [23]. For the nano-scale device dimension, the device experiences more current collapse due to the reduced gate-drain distance, which magnifies the surface traps effects. It is also very difficult to maintain uniform electric field distribution between the drain and gate space for obtaining a proper breakdown voltage as the device dimension scaled-down. A field plate gate structure effectively reduces the dispersion phenomena [24]. The field plate structure reduces the current collapse and enhances the breakdown voltage of the device by maintaining a low electric field at the gate to drain edge [25]. However, the field plate increasing the parasitic capacitance  $(C_{gd})$ , indicates the high-frequency performance (the current gain cut-off frequency  $f_t$  and the power gain cut-off frequency  $f_{max}$ ) of the device are limited due to  $(R_s + R_d)C_{gd}$  parasitic charging delay [26–28]. Therefore, the field plate technique limits the design of power amplifiers and MMICs for high-frequency bands such as V and W bands.

The objective of this work is to optimize the device structure for a simultaneous improvement of  $f_t/f_{max}$  and the breakdown voltage (V<sub>br</sub>). In this article, we propose a T-gate HfO<sub>2</sub>/InAlN/GaN/AlN on SiC substrate. The device surface is passivated by a high-*k* HfO<sub>2</sub> layer for improving the breakdown voltage of the device by reducing the parasitic capacitance (C<sub>gd</sub>). The graded InGaN n + source/drain region reduces the contact resistances. Introduction of high-*k* (high permittivity) passivation layer smoothens the electric field between the drain and the gate access region. The introduction of the AlN back-barrier suppresses the off-state subthreshold gate and drain leakage currents, thereby enhancing the breakdown voltage of the device.

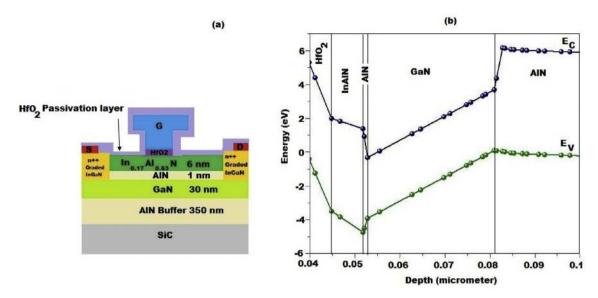

# 2. HfO<sub>2</sub>/InAIN/GaN/AIN MOS-HEMT device description and band diagram

The cross-section view of the proposed HfO<sub>2</sub>/InAlN/AlN/GaN MOSHEMT is shown in Fig. 1(a). The MOSHEMT consists of 350 nm AlN buffer, 30 nm GaN channel, 6 nm In<sub>0.13</sub>Al<sub>0.83</sub>N barrier and 3 nm high dielectric constant  $HfO_2$  as an oxide layer (k~20–25). The  $HfO_2$ oxide layer is used in this MOS-HEMT for controlling the gate leakage current and for the high breakdown voltage [29]. The near lattice-matched In<sub>0.13</sub>Al<sub>0.83</sub>N/GaN heterostructures offer a high two-dimensional electron gas density with high mobility [30]. An 1 nm AlN wide-bandgap (6.02 eV) spacer layer is sandwiched between the barrier and channel layer for improving the electron concentration in the two-dimensional electron gas (2DEG). The alloy scattering is lowered because of the AIN binary compound and also the quantum well depth is increased. As a result, the electron mobility in the channel is increased, thus improving the current [31]. The large bandgap AlN binary compound used as a buffer in this work, which provides larger polarization fields and an effective band offset, allowing for the aggressive scaling of the device dimensions and maximum 2DEG confinement, as compared to a conventional GaN or an AlGaN buffer. The high thermal conductivity (~340 W/mK) of AlN provides a good thermal management [32]. A 50 nm graded n + InGaN (Si ~  $2 \times 10^{19}$  cm<sup>-3</sup>) source and the drain region are formed for low contact resistances. A distance between the source and the drain is 270 nm, and a Ti/Au (50/50 nm) metal stack is used as ohmic contacts. A T-shaped gate with 30 nm foot length (Lg) and 2 × 20 µm gate width (w), 140 nm stem height and 400 nm head size is designed, which lift-off a wide cross-sectional gate area with small gate lengths for alleviating the gate using a Ni/Au (50/50 nm) stack. A 40 nm HfO<sub>2</sub> passivation layer is deposited over the device surface for low parasitic capacitances. A high ~ *k* passivation layer unfastens the dispersion effects which provides a root to achieve the good transport property in the 2DEG.

A TCAD simulation-based energy band diagram is shown in Fig. 1(b). As shown in the band diagram, the InAlN/AlN/GaN/AlN quantum well creates a high conduction band-offset and increases the quantum well depth for formation at the top of AlN/GaN heterojunction. The high-*k* HfO<sub>2</sub> insulating layer creates a 2.3 eV conduction band-offset (CBO) with InAlN, which helps in suppressing the gate leakage current more effectively as compared to other low-*k* insulator based MOS-HEMTs. AlN back-barrier mitigates the buffer leakage currents by offering large barrier height. At room temperature the simulation results have shown 2DEG (n<sub>s</sub>) of  $5.3 \times 10^{13}$  cm<sup>-2</sup> and carrier mobility (µ) of 1256 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for the proposed HEMT structure.

## 3. Results and discussion

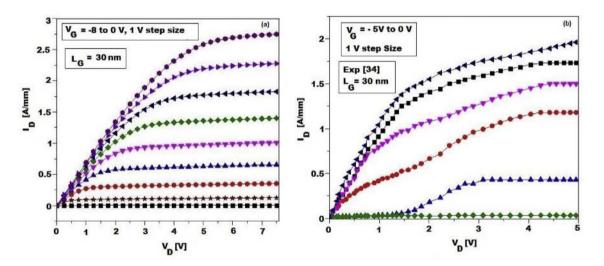

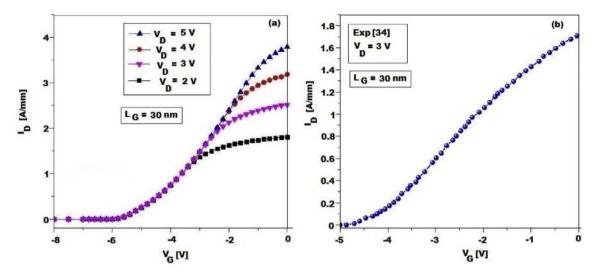

The drain current (DC) characteristics of the 30 nm gate length HfO<sub>2</sub>/InAlN/GaN/AlN based heterostructure are shown in Fig. 2(a). The simulated device delivers a peak current density of 2.7 A/mm for  $V_{gs} = 0$  V. The output conductance  $(g_{ds})$  of 35 mS/mm extracted from the saturation region of the output characteristics. The obtained result is superior to that of a rectangular gate SiO<sub>2</sub>/InAlN/ GaN HEMT without back-barrier structure [34], as shown in Fig. 2(b). The simulation results for the transfer characteristics of the proposed HfO<sub>2</sub>/InAlN/GaN/AlN HEMT and the experimentally fabricated SiO<sub>2</sub>/InAlN/GaN MOS-HEMT [34] are shown in Fig. 3(a) and Fig. 3 (b), respectively. The extracted threshold voltage (V<sub>th</sub>) of the proposed HEMT device is -5.8 V from the linear scale plot. At  $V_{ds} = 3$  V, the proposed T-gate HfO<sub>2</sub>/InAlN/GaN/AlN HEMT yielded 2.5 A/mm at a zero gate bias, whereas the 1.7 A/mm drain current density was demonstrated by a rectangular gate SiO<sub>2</sub>/InAlN/GaN MOS-HEMT without back-barrier [34].

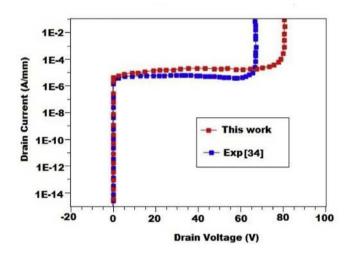

High power operation of the nano-scale III-Nitride at millimetre-wave spectrum can be ensured by suppressing the leakage currents in the device. This prevents the device from suboptimal breakdown and helps the device achieve a higher breakdown voltage. Buffer leakage current is reduced by the AlN blocking layer (buffer) and HfO<sub>2</sub> high-*k* gate dielectric minimizes the gate leakage current. The proposed HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT breakdown analysis is shown in Fig. 4. The device exhibited an off-state breakdown voltage of 81 V for Lg ~30 nm. Rectangular gate SiO<sub>2</sub>/InAlN/GaN MOS-HEMT without back-barrier exhibited a 61 V breakdown voltage for Lg ~30 nm.

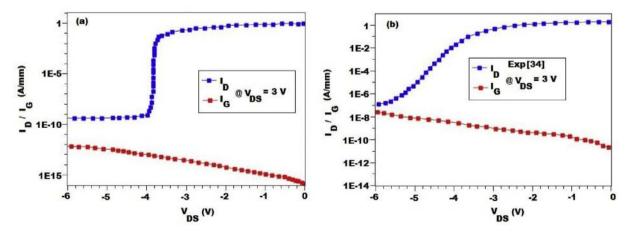

The off-state leakage current for the proposed ultra scaled HfO<sub>2</sub>/ InAlN/GaN/AlN MOS-HEMT is reduced to ~10<sup>-11</sup> A/mm using a high-*k* dielectric HfO<sub>2</sub> insulator, as shown in Fig. 5(a) and a subthreshold slope (SS) of 35 mV/decade is extracted from the logscale plot at V<sub>d</sub> = 3 V and V<sub>g</sub> swept from -6 V to 0 V. A good I<sub>on</sub>/ I<sub>off</sub> ratio of 10<sup>9</sup>, which is superior to that of a conventional GaN channel based MOS-HEMT [34] shown in Fig. 5(b), resulting from the ultra-thin InAlN barrier (6 nm) with AlN superlative back-

Fig. 1. (a). A HEMT structure; (b) Bandgap diagram.

Fig. 2. (a) Drain current characteristics of the proposed HfO<sub>2</sub>/InAIN/GaN/AIN MOS-HEMT. (b) Drain current characteristics of the experimentally reported SiO<sub>2</sub>/InAIN/GaN MOS-HEMT [34].

barriers. Whereas, the rectangular gate structure SiO<sub>2</sub>/InAlN/GaN MOS-HEMT without back-barrier [34] experienced an off-state gate leakage current of ~ $10^{-7}$  and I<sub>on</sub>/I<sub>off</sub> ratio of  $10^{7}$  [34].

Despite tremendous research progresses that have been made during recent years, further increasing the frequency of the GaNbased HEMT for next-generation high speed and high power submillimeter wave device applications is still needed. The current gain frequency ( $f_t$ ) and the power gain ( $f_{max}$ ) cut-off frequency of the FET are expressed as follows [35]:

$$f_t = \frac{\frac{g_m}{(2\pi)}}{\left[C_{gs} + C_{gd} \cdot \left[1 + \frac{R_s + R_d}{R_{ds}}\right] + C_{gd} \cdot g_m \cdot (R_s + R_d)\right]}$$

(1)

$$\tau = \frac{1}{2\pi f_t} = \frac{C_{gs} + C_{gd}}{g_m} + C_{gd} \cdot (R_s + R_d) \cdot \left[1 + \left(1 + \frac{C_{gs}}{C_{gd}}\right) \frac{g_{ds}}{g_m}\right]$$

(2)

$$f_{max} = \frac{f_t}{2\sqrt{(R_s + R_g)g_{ds} + 2\pi f_t R_g C_{gd}}}$$

(3)

For high power gain with high-frequency operation,  $f_{max}$  is a primary source. For enhancing  $f_{max}$ , the parasitic resistances such as gate resistance ( $R_g$ ), drain resistance ( $R_d$ ), source resistance ( $R_s$ ), gate to drain capacitance ( $C_{gd}$ ), and gate-source capacitance ( $C_{gs}$ ) need to be reduced.

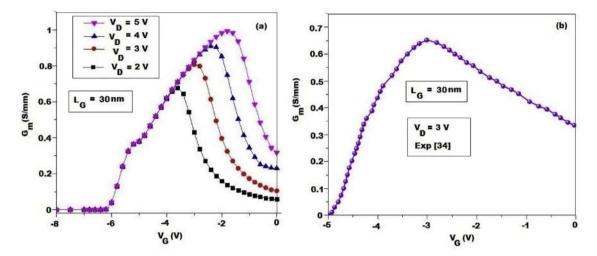

An ultra-scaled device with the T-gate HfO<sub>2</sub>/InAlN/GaN/AlN heterostructure with HfO<sub>2</sub> passivation is beneficial for enhancing transconductance and high-frequency operation of GaN-based HEMTs by minimizing the parasitic resistances ( $R_g$ ) and capacitances ( $C_{gs} + C_{gd}$ ). The simulation result of the transconductance variation with gate bias is displayed in Fig. 6 (a) and the maximum of 0.92 S/mm reached at  $V_g = -1.8$  V, whereas, the rectangular gate structure SiO<sub>2</sub>/InAlN/GaN MOS-HEMT without back-barrier recorded 0.653 S/mm [34] is depicted in Fig. 6 (b).

The extracted parameters from the small-signal equivalent circuits of HEMT, transconductance  $(g_m)$ , drain conductance  $(g_{ds})$ ,

Fig. 3. (a) Transfer characteristics of the proposed HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT; (b) Transfer characteristics of the experimentally reported SiO<sub>2</sub>/InAlN/GaN MOS-HEMT [34].

**Fig. 4.** Simulation result of the breakdown characteristics of the proposed HfO<sub>2</sub>/InAlN/ GaN/AlN MOS-HEMT in comparison with the breakdown characteristics of SiO2/InAlN/ GaN MOS-HEMT [34].

gate-source capacitance ( $C_{gs}$ ), gate-drain capacitance ( $C_{gd}$ ), source resistance ( $R_s$ ), drain resistance ( $R_d$ ), Sheet resistance ( $R_{sh}$ ) and on resistance ( $R_{on}$ ) of the 30 nm T-gate HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT with n + source and drain regions are 0.92 S/mm, 35 mS/mm, 572 fF/mm, 84 fF/mm, 0.12  $\Omega$ -mm, 0.15  $\Omega$ -mm, 421  $\Omega$ /sqr and 0.32  $\Omega$ -mm, respectively.

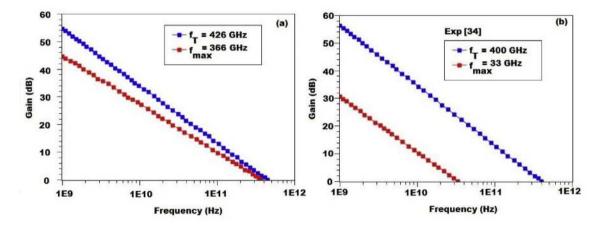

The small-signal gain characteristics of the T-gate HfO<sub>2</sub>/InAlN/ GaN/AlN MOS-HEMT is displayed in Fig. 7(a) at a peak  $g_m$  gate bias. A maximum cut-off frequency  $f_t/f_{max}$  of 426/366 GHz obtained by extrapolating current gain and power gain. The rectangular gate structure SiO<sub>2</sub>/InAlN/GaN MOS-HEMT without back-barrier demonstrated  $f_t/f_{max}$  of 400/33 GHz [34], as shown in Fig. 7(b).

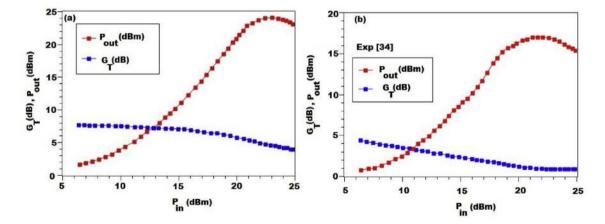

The large-signal analysis of the T-gate HfO<sub>2</sub>/InAIN/GaN/AIN MOS-HEMT is performed for 30 GHz, and the corresponding input power (dBm), output power (dBm), and power gain (dB) relationship are displayed in Fig. 8(a). The rectangular gate structure SiO<sub>2</sub>/InAIN/GaN MOS-HEMT large-signal characteristics are also displayed in Fig. 8(b) for comparison.

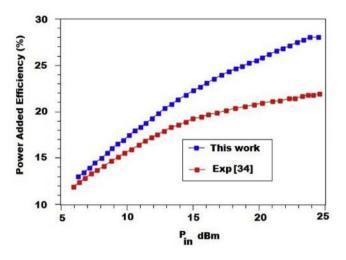

The power-added efficiency (PAE) (%) variation with input power is displayed in Fig. 9 for the T-gate  $HfO_2/InAIN/GaN/AIN$  MOS-HEMT. Simulation results show that the maximum power-added

Fig. 5. (a) Gate leakage and drain leakage current characteristics of the proposed HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT. (b) Gate leakage and drain leakage current characteristics of the experimentally studied SiO<sub>2</sub>/InAlN/GaN MOS-HEMT [34].

Fig. 6. (a) Transconductance variation with gate bias for the proposed HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT. (b) Transconductance variation with gate bias for the previously reported SiO<sub>2</sub>/InAlN/GaN MOS-HEMT [34].

Fig. 7. (a) Small-signal characteristics of the proposed Hf02/InAlN/GaN/AIN MOS-HEMT. (b) Small-signal characteristics of the experimentally reported SiO2/InAlN/GaN MOS-HEMT [34].

Fig. 8. (a) Large-signal performance of the proposed HfO<sub>2</sub>/InAIN/GaN/AIN MOS-HEMT. (b) Large-signal performance of the SiO<sub>2</sub>/InAIN/GaN MOS-HEMT [34].

efficiency of 28% demonstrated by the proposed MOS-HEMT. 21% of power added efficiency (PAE) was obtained from the SiO<sub>2</sub>/InAlN/ GaN MOS-HEMT [34].

The proposed T-gate HfO<sub>2</sub>/InAlN/GaN/AlN MOS-HEMT enables very low output conductance ( $g_{ds}$ ), suppressed short channel effect (SS), good  $I_{on}/I_{off}$  ratio, improved breakdown voltage ( $V_{br}$ ), low

Fig. 9. Power added efficiency of the proposed  $HfO_2/InAlN/GaN/AlN$  MOS-HEMT in comparison with that of SiO\_2/InAlN/GaN MOS-HEMT [34].

leakage current (Ig), and a significant improvement in small signal and large signal characteristics. Moreover, the current collapse and kink effects are not found in the DC characteristics of the proposed MOS-HEMT. The cut-off frequencies are enhanced by T-shape with a tall stem gate structure, which offered additional gate structure and reduced gate resistance and capacitance.

### 4. Conclusion

The HfO<sub>2</sub>/InAlN/AlN/GaN MOS-HEMT for high power millimetre-wave applications has been proposed, and its DC, RF and high power characteristics have been analyzed using the physicsbased Silvaco ATLAS TCAD. The T-gated InAlN/GaN HEMT with AlN back-barrier improves the device performance as a result of the enhanced breakdown, small-signal and large-signal characteristics. The optimized device structure achieved the high current density, low leakage current and high Ion/Ioff ratio. The power and frequency characterization of the device proved its exemplary performance through the achievement of the excellent off-state breakdown voltage of 81 V, and  $f_t/f_{max}$  of 426/366 GHz. The large signal analysis of the HEMT stack performed at 30 GHz yielded a maximum poweradded efficiency of 24%. The high-performance simulation results (JFoM = 34.506 THz V and  $(f_t.f_{max})^{1/2}$  = 394.86 GHz) indicate that the proposed HfO2/InAIN/GaN/AIN based III-Nitride HEMT is a suitable device for modern high power millimeter-wave electronics.

### References

- [1] Y.-F. Wu, A. Saxler, M. Moore, R.P. Smith, S. Sheppard, P.M. Chavarkar, T. Wisleder, U.K. Mishra, P. Parikh, 30-W/mm GaN HEMTs by field plate optimization, IEEE Electron. Device Lett. 25 (2004) 117–119, https://doi.org/ 10.1109/LED.2003.822667.

- M. Higashiwaki, T. Mimura, T. Matsui, Millimeter-wave GaN HFET technology, Proc. SPIE (2008) 6894, https://doi.org/10.1117/12.767574.

X.A. Cao, H. Piao, J. Li, J.Y. Lin, H.X. Jiang, Surface chemical and electronic

- [3] X.A. Cao, H. Piao, J. Li, J.Y. Lin, H.X. Jiang, Surface chemical and electronic properties of plasma-treated n-type Al0.5Ga0.5N, Phys.Stat. Sol. A 204 (2007) 3410–3416, https://doi.org/10.1002/pssa.200723119.

- [4] F. Medjdoub, J.F. Carlin, M. Gonschorek, E. Feltin, M.A. Py, D. Ducatteau, C. Gaquiere, N. Grandjean, E. Kohn, Can InAlN/GaN be an alternative to high power/high temperature AlGaN/GaN devices? IEDM Tech. Dig. (2006) 673, https://doi.org/IEDM.2006.346935.

- [5] R. Butte, J.-F. Carlin, E. Feltin, M. Gonschorek, S. Nicolay, G. Christmann, D. Simeonov, A. Castiglia, J. Dorsaz, H.J. Buehlmann, S. Christopoulos, H. von Högersthal, A.J.D. Grundy, M. Mosca, C. Pinquier, M.A. Py, F. Demangeot, J. Frandon, P.G. Lagoudakis, J.J. Baumberg, N. Grandjean, Current status of AllnN layers lattice matched to GaN for photonics and electronics, J. Phys. D Appl. Phys. 40 (2007) 6328, https://doi.org/10.1088/0022-3727/40/20/S16.

- [6] S. Keller, S. Heikman, L. Shen, I.P. Smorchkova, S.P. DenBaars, U.K. Mishra, GaN–GaN junctions with ultrathin AlN interlayers: expanding heterojunction design, Appl. Phys. Lett. 80 (2002) 4387, https://doi.org/10.1063/1.1484551.

- [7] L. Michael, Gate-recessed integrated E/D GaN HEMT technology with fT/fmax >300 GHz, IEEE Electron. Device Lett. 34 (2013) 741–743, https://doi.org/ 10.1109/LED.2013.2257657.

- [8] F. Medjdoub, Barrier-layer scaling of InAlN/GaN HEMTs, IEEE Electron. Device Lett. 29 (2008) 422–425, https://doi.org/10.1109/LED.2008.919377.

- [9] A. Crespo, High-power Ka-band performance of AllnN/GaN HEMT with 9.8nm-thin barrier, IEEE Electron. Device Lett. 31 (2010) 2–4, https://doi.org/ 10.1109/LED.2009.2034875.

- [10] S. Tirelli, AlInN-based HEMTs for large-signal operation at 40 GHz, IEEE Trans. Electron. Dev. 60 (2013) 3091–3098, https://doi.org/10.1109/ TED.2013.2262136.

- [11] J. Kuzmík, A. Kostopoulos, G. Konstantinidis, J.-F. Carlin, A. Georgakilas, D. Pogany, InAlN/GaN HEMTs: a first insight into technological optimization, IEEE Trans. Electron. Dev. 53 (2006) 422–426, https://doi.org/10.1109/ TED.2013.2262136.

- [12] S. Tirelli, D. Marti, H. Sun, A.R. Alt, J.-F. Carlin, N. Grandjean, C.R. Bolognesi, Fully passivated AllnN/GaN HEMTs with ft/fMAX of 205/220 GHz, IEEE Electron. Device Lett. 32 (2011) 1364–1366, https://doi.org/10.1109/ LED.2011.2162087.

- [13] J.W. Chung, T.-W. Kim, T. Palacios, Advanced gate technologies for state-ofthe-art fT in AlGaN/GaN HEMTs, IEDM Tech. Dig. (2010), https://doi.org/ 10.1109/IEDM.2010.5703449.

- [14] J.W. Chung, W.E. Hoke, E.M. Chumbes, T. Palacios, AlGaN/GaN HEMT with 300-GHz fmax, IEEE Electron. Device Lett. 31 (2010) 195–197, https://doi.org/ 10.1109/LED.2009.

- [15] Ronghua Wang, Guowanf, Oleg Laboutin, Wayne Johnson, 210-GHz InAlN/ GaN HEMTs with Dielectric free passivation, IEEE Electron. Device Lett. 32 (2011) 892–894, https://doi.org/10.1109/LED.2011.2147753.

- [16] Z. Hu, Y. Yue, M. Zhu, B. Song, S. Ganguly, J. Bergman, D. Jena, H.G. Xing, Impact of CF4 plasma treatment on threshold voltage and mobility in Al2O3/InAIN/ GaN MOSHEMTs, Appl. Phys. Exp. 7 (2014), https://doi.org/10.7567/ APEX.7.031002.

- [17] Hong Zhou, Xiabing Lou, Nathan J. Conrad, Mengwei Si, Heng Wu, Sami Alghamdi, Shiping Guo, Roy G. Gordon, Peide D. Ye, High-performance InAlN/GaN MOSHEMTs enabled by atomic layer epitaxy MgCaO as gate dielectric, IEEE Electron. Device Lett. 37 (2016) 556–559, https://doi.org/ 10.1109/LED.2016.2537198.

- [18] S. Liu, S. Yang, Z. Tang, Q. Jiang, C. Liu, M. Wang, K.J. Chen, Al2O3/AlN/GaN MOS-channel-HEMTs with an AlN interfacial layer, IEEE Electron. Device Lett. 35 (2014) 723–725, https://doi.org/10.1109/LED.2014.2322379.

- [19] X. Sun, O.I. Saadat, K.S. Chang-Liao, T. Palacios, S. Cui, T.P. Ma, Study of gate oxide traps in Hf02/AlGaN/GaN metal-oxidesemiconductor high-electronmobility transistors by use of AC transconductance method, Appl. Phys. Lett. 102 (2013), https://doi.org/10.1063/1.4795717.

- [20] S. Yang, S. Huang, H. Chen, C. Zhou, Q. Zhou, M. Schnee, Q.-T. Zhao, J. Schubert, K.J. Chen, AlGaN/GaN MISHEMTs with high-κ LaLuO3 gate dielectric, IEEE Electron. Device Lett. 33 (2012) 979–981, https://doi.org/10.1109/ LED.2012.2195291.

- [21] H.-C. Chiu, J.-H. Wu, C.-W. Yang, F.-H. Huang, H.-L. Kao, Low-frequency noise in enhancement-mode GaN MOS-HEMTs by using Stacked Al2O3/Ga2O3/ Gd2O3 gate dielectric, IEEE Electron. Device Lett. 33 (2012) 958–960, https:// doi.org/10.1109/LED.2012.2194980.

- [22] S. Ganguly, J. Verma, G. Li, T. Zimmermann, H. Xing, D. Jena, Presence and origin of interface charges at atomic-layer deposited Al2O3/III-nitride heterojunctions, Appl. Phys. Lett. 99 (2011), https://doi.org/10.1063/ 1.3658450.

- [23] R. Vetury, N.-Q. Zhang, S. Keller, U.K. Mishra, The impact of surface states on the DC and RF characteristics of AlGaN–GaN HFETs, IEEE Trans. Electron. Dev. 48 (2001) 560–566, https://doi.org/10.1109/16.906451.

- [24] Y. Ando, Y. Okamoto, H. Miyamoto, T. Nakayama, T. Inoue, M. Kuzuhara, 10-W/mm AlGaNGaN HFET with a field modulating plate, IEEE Electron. Device Lett. 24 (2003) 289–291, https://doi.org/10.1109/LED.2003.812532.

- [25] Huolin Huang, Yung C. Liang, Ganesh S. Samudra, Ting-Fu Chang, Chih-Fang Huang, Effects of gate field plates on the surface state related current collapse in AlGaN/GaN HEMTs, IEEE Trans. Power Electron. 29 (2014) 2164–2173, https://doi.org/10.1109/TPEL.2013.2288644.

- [26] T. Palacios Nidhi, A. Chakraborty, S. Keller, U.K. Mishra, Study of impact of access resistance on high-frequency performance of GaN HEMTs by measurements at low temperature, IEEE Electron. Device Lett. 27 (2006) 877–880, https://doi.org/10.1109/LED.2006.884720.

- [27] P.J. Tasker, B. Hughes, Importance of source and drain resistance to the maximum ft of millimeter-wave MODFETs, IEEE Electron. Device Lett. 10 (1989) 291–293, https://doi.org/10.1109/55.29656.

- [28] C.R. Bolognesi, A.C. Kwan, D.W. DiSanto, Transistor delay analysis and effective channel velocity extraction in GaN HFETs, IEDM Tech. Dig. (2002), https:// doi.org/10.1109/IEDM.2002.1175931.

- [29] Kefeng Han, Lin Zhu, GaN MOSHEMT employing HfO<sub>2</sub> as a gate dielectric with partially etched barrier, Semicond. Sci. Technol. 32 (2017), https://doi.org/ 10.1088/1361-6641/117be3.

- [30] A.V. Lundin Sakharov, W.V. Zavarin, E.E, Ultrathin barrier InAlN/GaN heterostructures for HEMTs, Semiconductors 52 (2018) 1843–1845, https://doi.org/ 10.1134/S1063782618140257.

- [31] P. Murugapandiyan, S. Ravimaran, J. William, DC and microwave characteristics of Lg 50 nm T-gate InAIN/AIN/GaN HEMT for future high power RF applications, Int. J. Electron. Commun. (AEÜ) 77 (2017) 163–168, https:// doi.org/10.1016/j.aeue.2017.05.004.

- [32] R. Rounds, B. Sarkar, A. Klump, C. Hartmann, T. Nagashima, R. Kirste, A. Franke, M. Bickermann, Y. Kumagai, Z. Sitar, R. Collazo, Thermal conductivity of single-crystalline AlN, Appl. Phys. Express (2018) 11, https://doi.org/10.7567/ APEX.11.071001.

- [33] Jinhai Shao, Jianan Deng, W. Lu, Yifang Chen, Nanofabrication of 80 nm asymmetric T shape gates for GaN HEMTs, Microelectron. Eng. 189 (2018) 6–10, https://doi.org/10.1016/j.mee.2017.12.001.

- [34] Yuanzheng Yue, Zongyang Hu, Jia Guo, Berardi Sensale-Rodriguez, Guowang Li, Ronghua Wang1, Faiza Faria, Bo Song, Xiang Gao, Shiping Guo, Thomas Kosel, Gregory Snider, Patrick Fay, Debdeep Jena, Huili Grace Xing, Ultrascaled InAIN/GaN high electron mobility transistors with cut off frequency of 400GHz, Jpn. J. Appl. Phys. 52 (2013), https://doi.org/10.7567/ JJAP.5208JN14.

- [35] Paul J. Tasker, Brian Hughes, Importance of source and drain resistance to the maximum fT of millimeter-wave MODFET's, IEEE Electron. Device Lett. 10 (1989) 291–293, https://doi.org/10.1109/55.29656.